Exercícios com Registradores de Deslocamento

- Projete um contador em Anel de 8 estados com base no CI 74HC194 (registrador de deslocamento universal; 4 x FF's). Supondo ainda que uma variável externa

Solução:

UM contador em anel exige um carregamento inicial de seus FF's. Não se pode simplesmente iniciar seu circuito com todos os seus FF's. resetados. Um "Master Reset" não no auxilia neste caso. Isto significa que devemos realizar a carga inicial com algum padrão diferente de '0' em todos os FF's (FF's resetados), ou seja, significa que necessitamos realizar um "Parallel Load" logo no início do funcionamento deste circuito.

No caso do 74HC194, o "Paralled Load" é síncrono e ocorre quando

Notamos também que:

- O "Shift Right" ocorre com

- O "Shitf Left" ocorre com

Por inspeção notamos que:

- Quando

- Quando

Já o sinal

Então podemos concluir que:

Lembrando que um circuito RC demora certo tempo carregar, o que implica que durante um curto período de tempo inicial, o nível lógico na saída do Capacitor estará BAIXO, ou seja, um circuito RC sozinho gera um sinal do inicialização do tipo

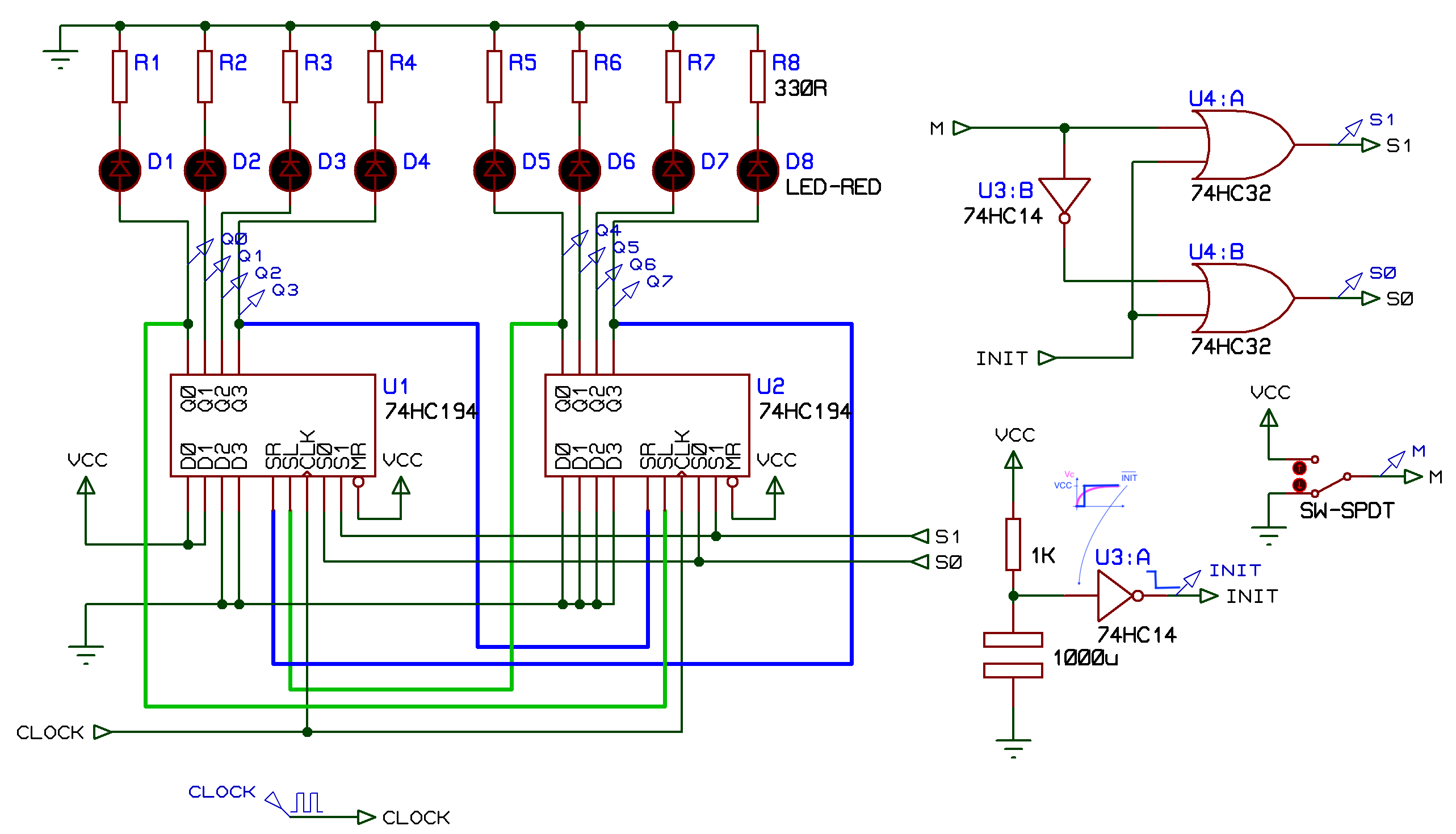

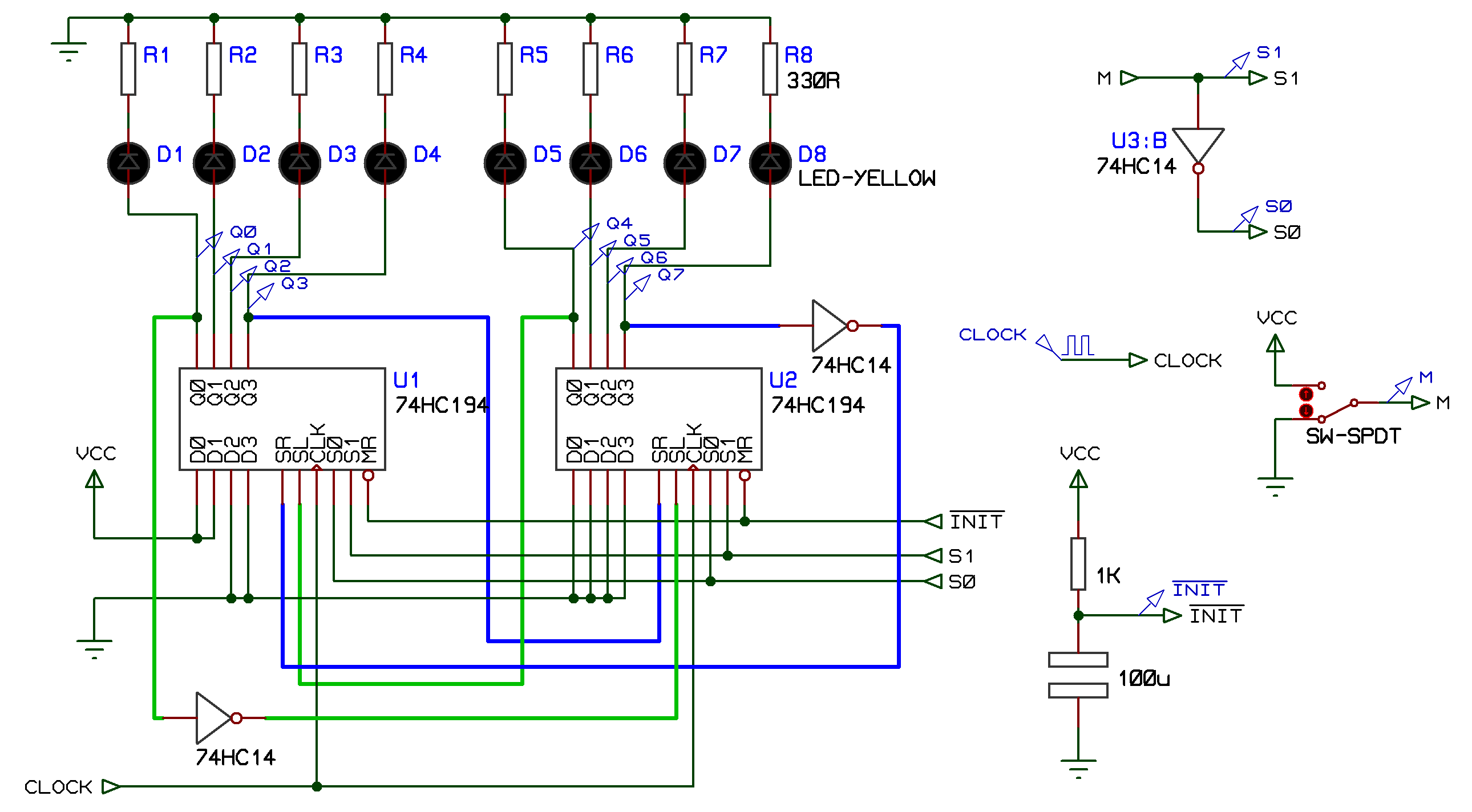

Circuito final: cont_anel_8_estados_bi_reg_74194.DSN :

Note no diagrama os cascateamentos de sinais necessários entre as 2 pastilhas 74HC194:

- As linhas ressaltadas em azul destacam os cascateamentos necessários para o "shit right";

- As linhas ressaltadas em verde destacam os cascateamentos necessários para o "shift left".

Note ainda que se preferiu realizar a carga paralela de dados com mais de 1 bit setado. No caso, as entradas foram ajustadas das seguinte forma:

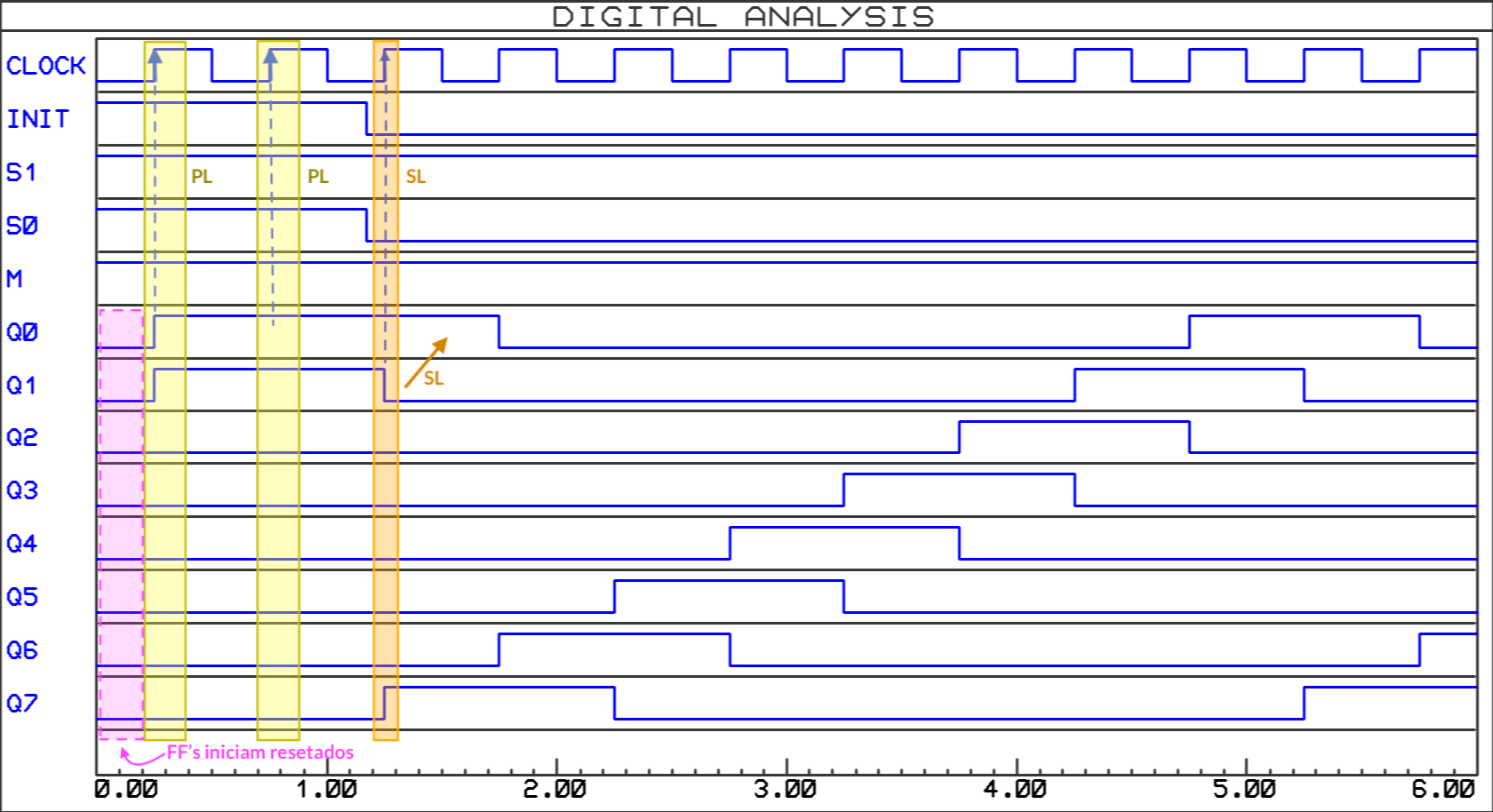

Circuito simulado:

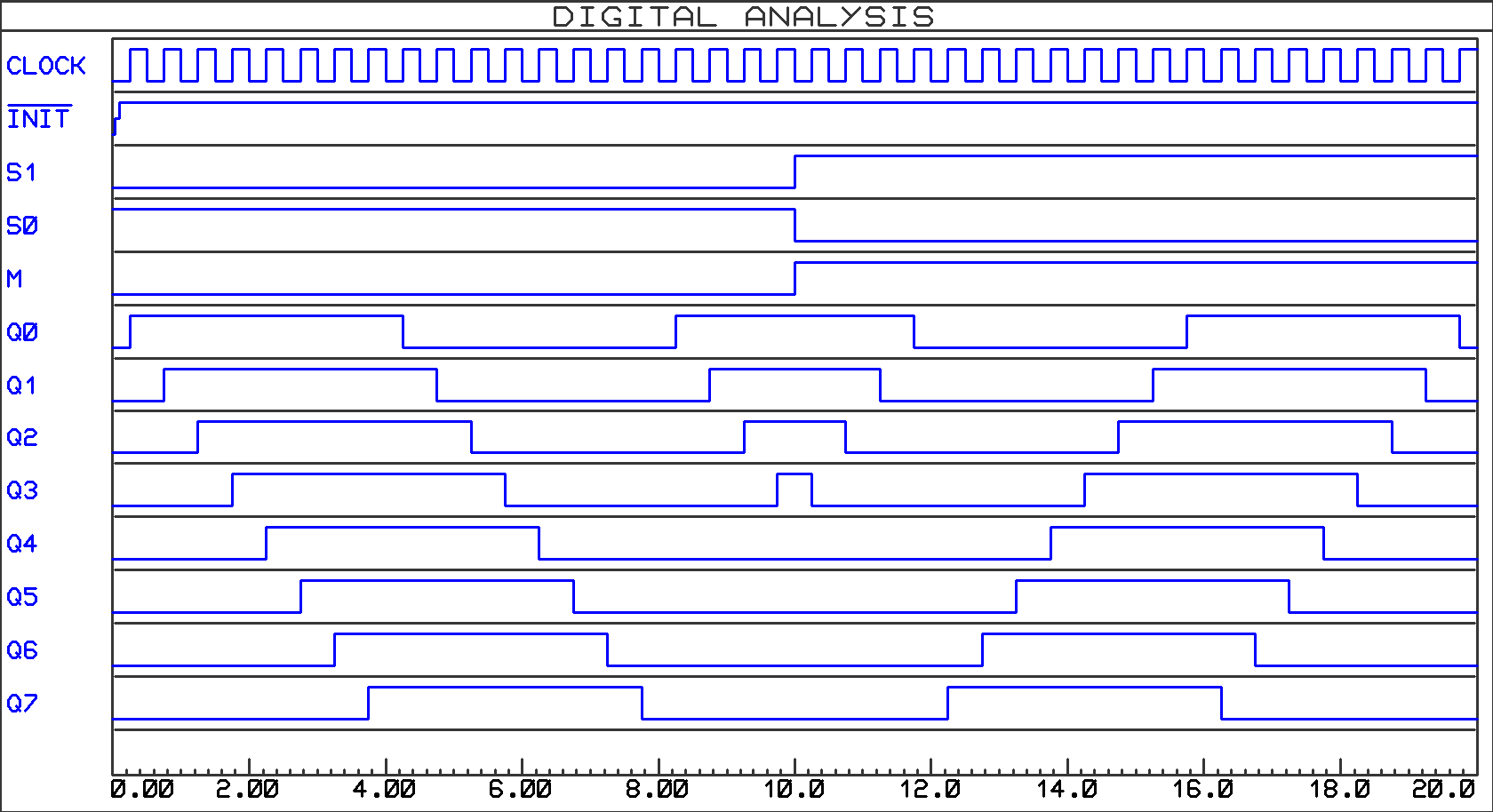

Algumas formas de onda:

Detalhe: repare no valor do Capacitor C1. Ele não pode ser um valor muito baixo, senão não será realizado o Parallel Load síncrono, necessário neste circuito. Note que para que o Parallel Load seja gerado é necessário que

Perceba na figura anterior, que a primeira borda de subida do sinal de CLOCK já ocorre com

- Projete um contador em Jonhson de 16 estados com base no CI 74HC194 (registrador de deslocamento universal; 4 x FF's). Supondo ainda que uma variável externa

Solução:

Para criar este contador, necessitamos:

Este circuito é mais fácil de desenvolver que o contador em Anel. Por inspeção notamos:

- Quando

- Qaundo

Este tipo de contador não exige nenhuma inicialização em particular, podendo seus FF's iniciarem resetados. Então podemos usar um sinal de "INIT" (a partir de um circuito RC) para gerar um sinal de "Master Reset". Apenas perceber que para a pastiulha 74HC194, o "Master Reset" deve ser ativo baixo.

Uma leve modificação no circuito anterior, e temos o novo circuito mostrado abaixo: cont_johnson_16_estados_bi_reg_74194.DSN

Notar que este contador é formado usando a saída invertida (complementar) de seu último FF. Motivo pelo qual, temos as portas invasoras nas saídas Q0 de U1 e Q3 de U2.

Simulação:

Segue figura com as formas de onda geradas por este tipo de circuito:

Note que neste caso, o sinal

Perceba que neste caso foi usado um capacitor menor que no caso anterior. Neste caso, basta que a constante de tempo RC seja aproximadamente igual à uns 20 ns, o tempo necessário para o Master Reset ser efetivado pela pastilha 74HC194 (parâmetro AC:

Fernando Passold, em 31/05/2022.