Conteúdo que falta:

- Exercícios com contadores usando FF's discretos;

- Estudar CI's contadores assíncronos: 7490, 7492 e 7493.

Exercícios da 1a-parte de contadores:

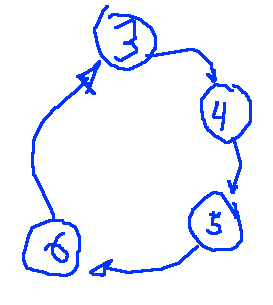

Ex_1) Contador assíncrono de 3 --> 6 (cíclico).

Projete um contador assíncrono capaz de realizar a seguinte sequencia de contagem:

Solução:

Maior contagem:

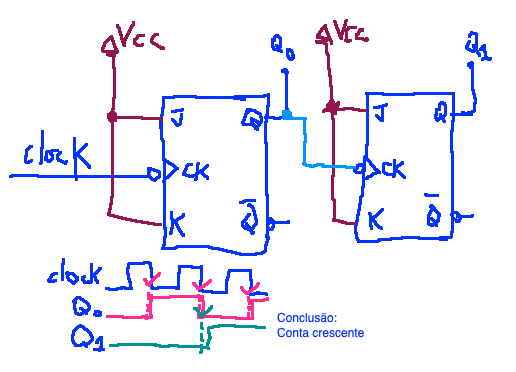

Qual FF usar?

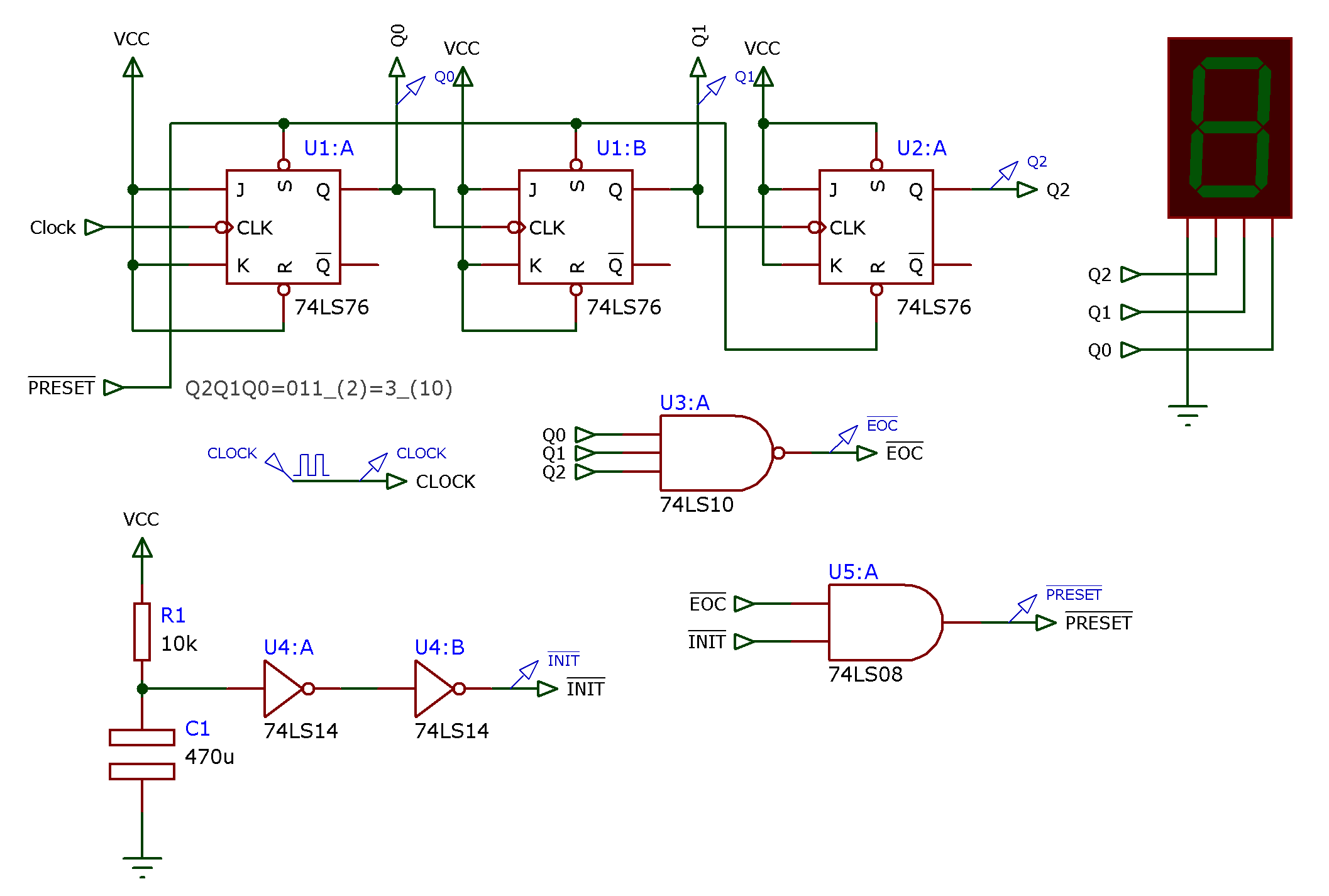

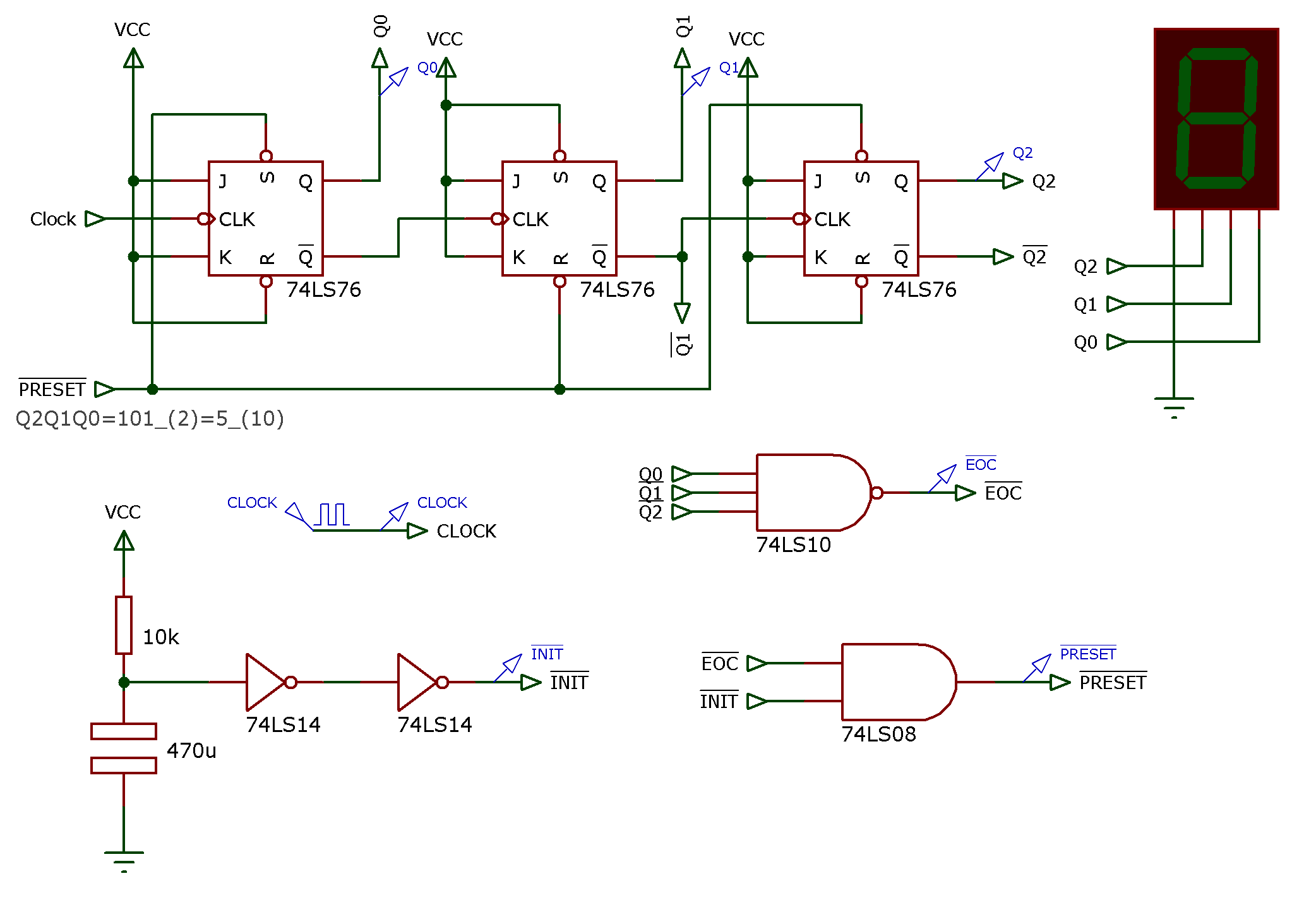

Usaremos o 74LS76 --> FF-JK, borda de subida ou de descida... --> Supondo que seja borda de descida.

Descobrindo a "arquitetura" (conexões) necessárias para formar um contador crescente:

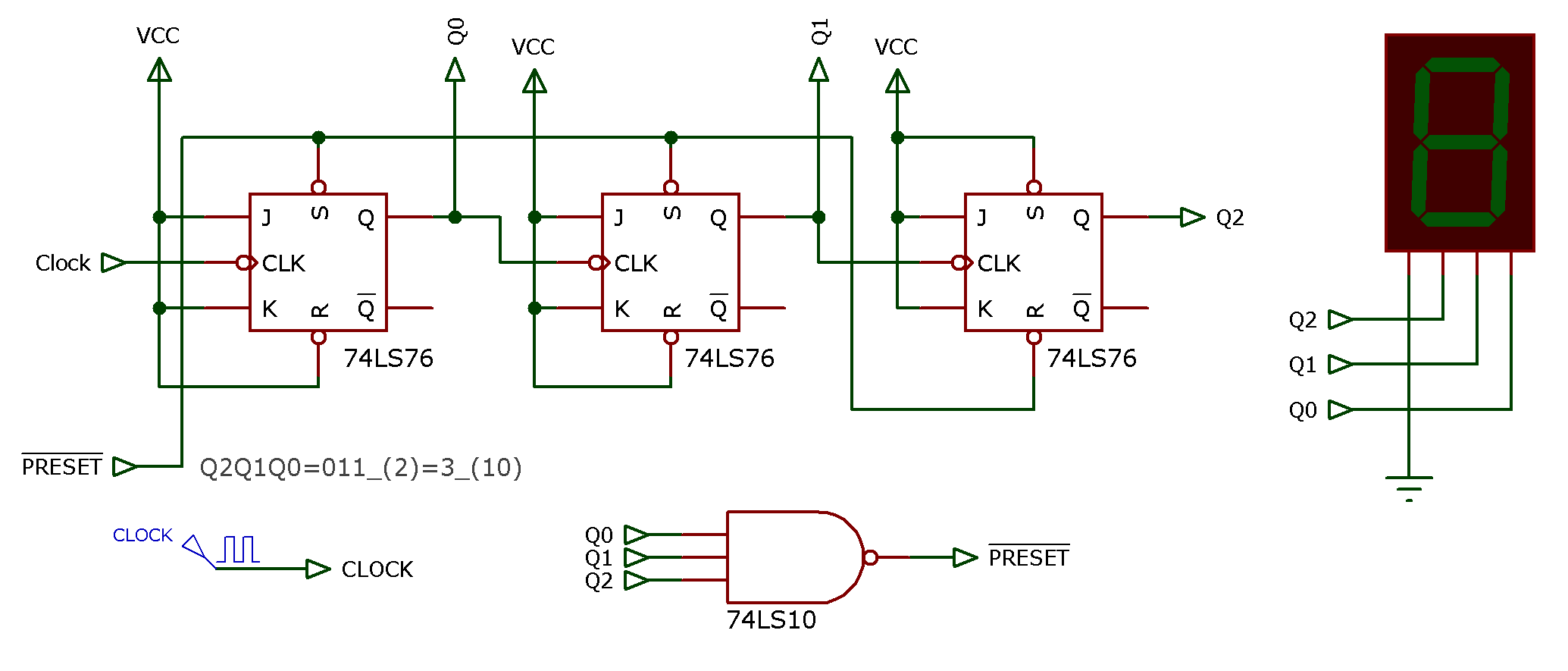

O circuito final usa 3 FF's.

Se não forem usadas entradas assíncronas, vamos ter contador "MOD-8": conta de 0 até 7 [ contador_assync_up_mod8.DSN ]:

.gif)

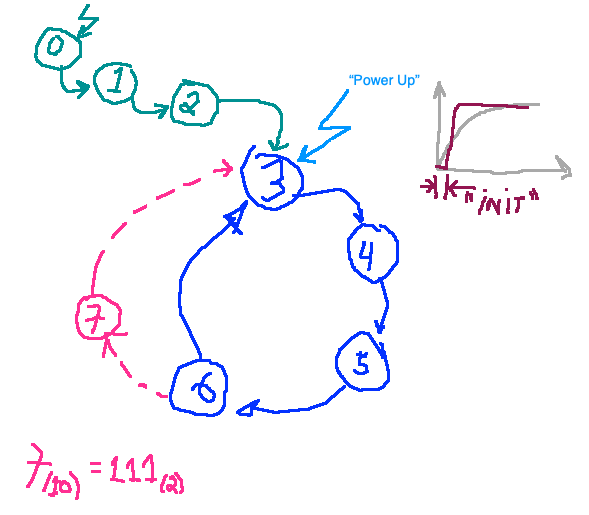

Redesenhando diagrama de estados para contagem desejada:

Como queremos que o circuito já inicie sob certa condição inicial (pulso de

Circuito: [ contador_assync_up_3_to_6.DSN ] -- 1a. versão, sem circuito de Preset no Power Up, isto é, circuito inicia contagem no número 0 avançando até o número 3 logo após sua alimentação; depois não conta mais os números 0, 1 e 2.

Vídeo:

2a-versão: com circuito de Power-Up que força Preset (estado inicial em 3): [ contador_assync_up_3_to_6_ve2.DSN ]

Animação:

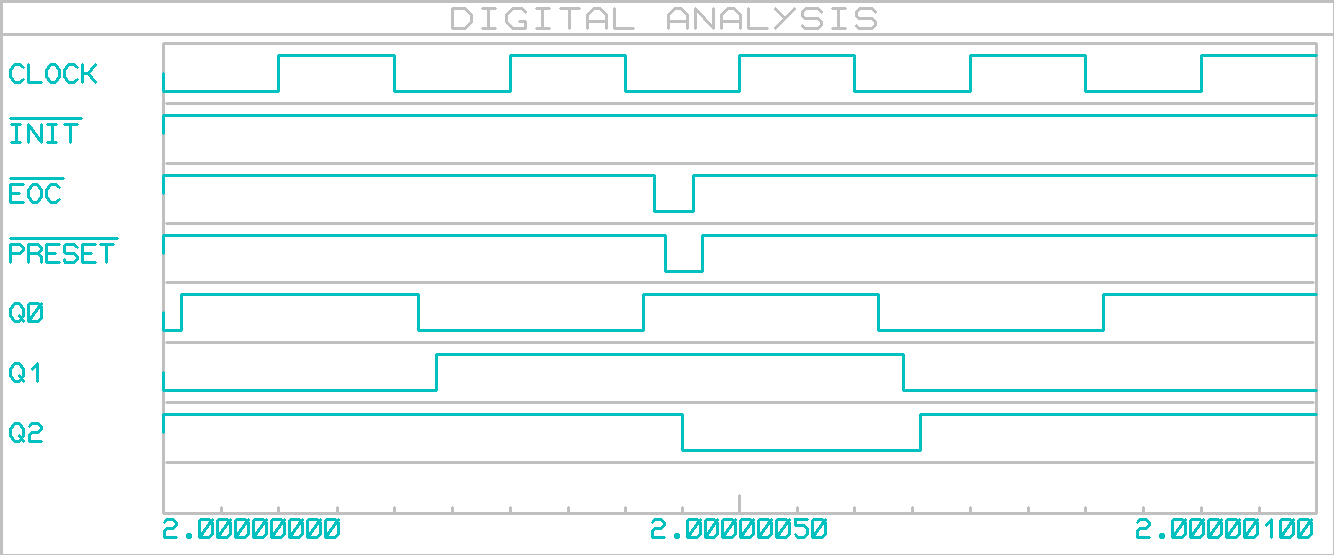

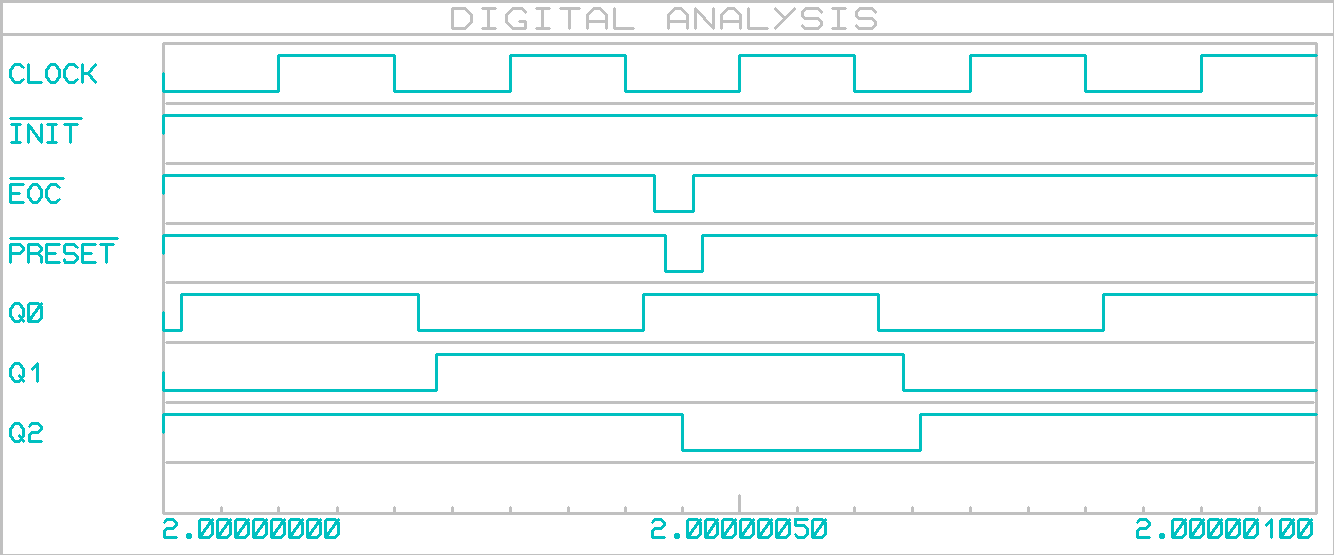

Formas de onda:

Obs.: Note que para exbir as formas de onda acima, o bloco de gerador de sinais (Clock) foi ajustado para gerar onda quadrada na frequência de 5 MHz (para ressaltar a duração dos sinais

E a janela (intervalo) de tempo usado para simulação também foi ajustado de forma a mostrar as formas de onda à partir de 2 segundos (depois que passou o intervalo de geração do sinal de

Ex_2: contador assíncrono de 5 --> 2 (cíclico).

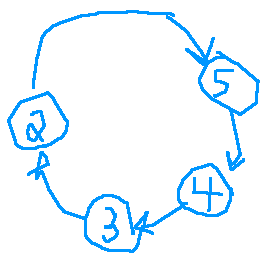

Agora projete outro circuito capaz de realizar a seguinte sequencia:

Solução:

Redesenhando o diagrama de estados:

REF | Q2Q1Q0----+-------7. | 1 1 16. | 1 1 05. | 1 0 14. | 1 0 03. | 0 1 12. | 0 1 01. | 0 0 10. | 0 0 0

Solução:

Circuito final: contador_assync_down_5_to_2_ve2.DSN :

Comentários:

- Note que o sinal de

- Note que o sinal

- Por fim, foi acrescentado um circuito de inicialização que gerar o sinal

Formas de onda:

Fernando Passold, em 03/09/2021