Contadores Assíncronos de Módulo n

[arquivo PDF (teoria)]

Seguem anotações/Comentários em sala de aula sobre tópico:

Análises/Respostas para circuitos ou problemas propostos em certos slides:

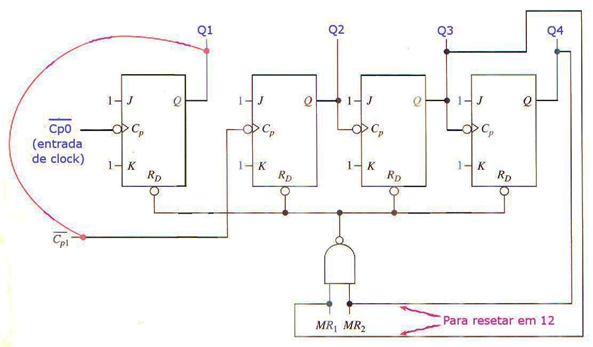

Slide 29: Contador módulo 12 --> 0 ~ 11

= contador divisor de frequência por 12.

Solução: usando 74LS93 (MOD-16: 0 ~ 15=F)

Reset ou "Master Reset" quando atinge o número

No CI: Q3=1; Q2=1; Q1=0 e Q0=0 (Na figura apresentada, detectar Q4 e Q3).

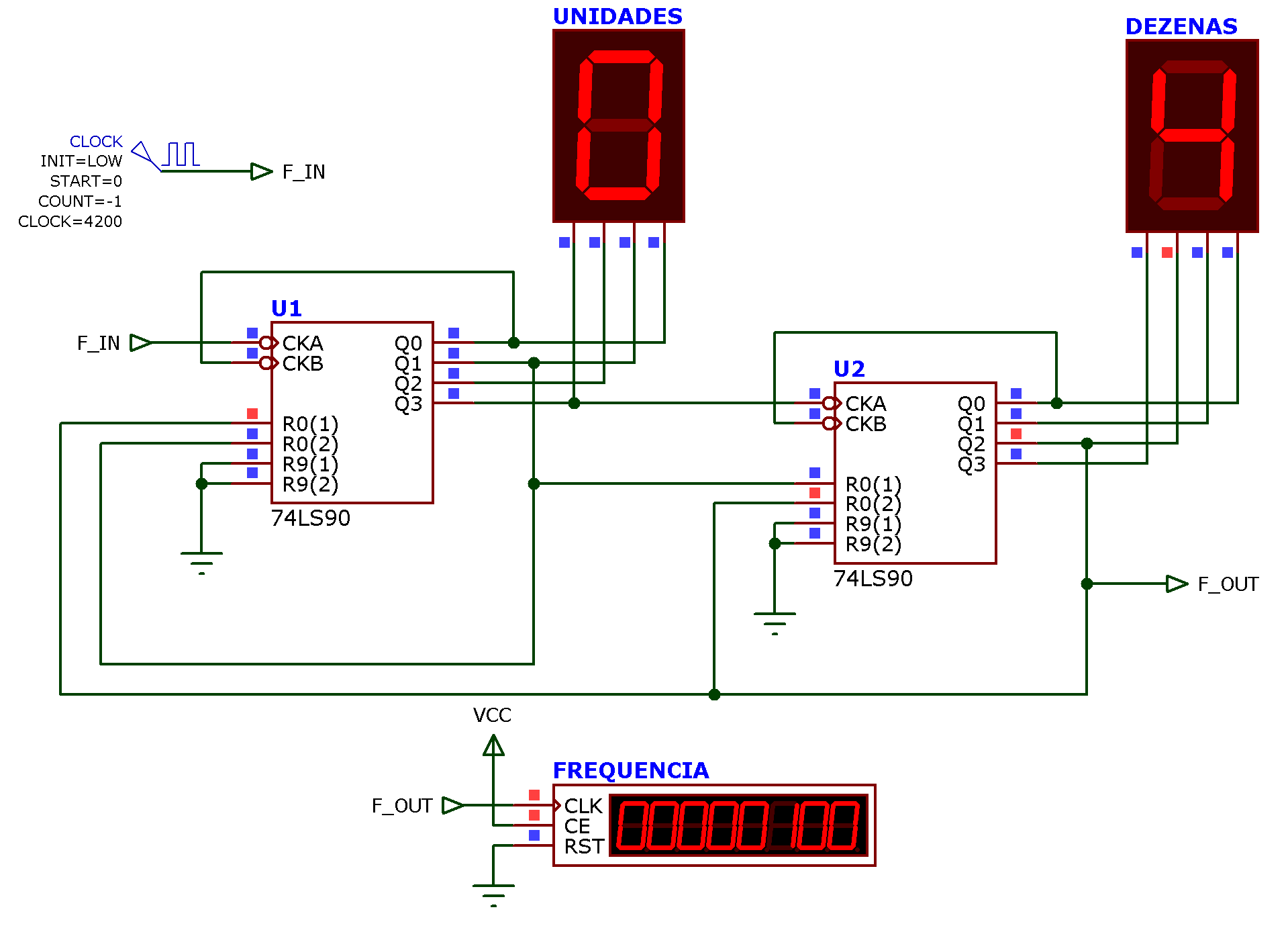

Slide 38: Exercício 3 --> Circuito divisor de frequência por 42.

Opção a) Usando CI 7490 --> 2 x 7490:

Etapa 1: Circuito contador ÷ 100 [circuito: contador_MOD_100_74LS90.DSN ]

Etapa 2: Programar um "Master Reset" quando contagem atinge

Circuito final: contador_div42_74LS90.DSN

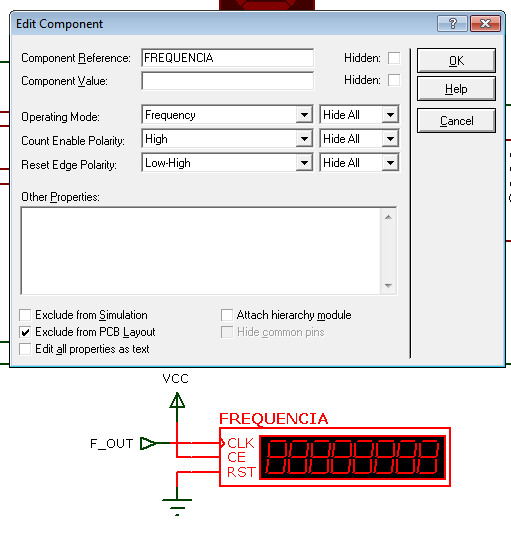

Obs.: para mostrar o Frequência no Proteus:

Na aba lateral esquerda, selecione "Instrumentos" e entre os instrumentos, selecione: "Counter Timer":

Arraste este instrumento até o ponto desejado no diagrama elétrico e modifique suas propriedades do padrão "Time (secs)" para "Frequency":

Propriedade "default" Ajuste para Frequencímetro

Note que é necessário "habilitar" este instrumento. Ajustando a entrada CE = Count Enable e desativando a entrada RST = Reset.

Determinando "duty-cycle" do circuito anterior:

Parte da Tabela verdade do contador:

xxxxxxxxxxSaídas U2: | Saídas U1: | ResultadoQ3 Q2 Q1 Q0 | Q3 Q2 Q1 Q0 | contagem-----------------+------------------+--------------------0 0 0 0 | 0 0 0 0 | 00 0 0 0 | 0 0 0 1 | 1: | : | :0 0 1 1 | 1 0 0 1 | 390 1 0 0 | 0 0 0 0 | 400 1 0 0 | 0 0 0 1 | 410/0 1/0 0/0 0/0 | 0/0 0/0 1/0 0/0 | 42/0 - Instante do recycle

Note:

Reparo que

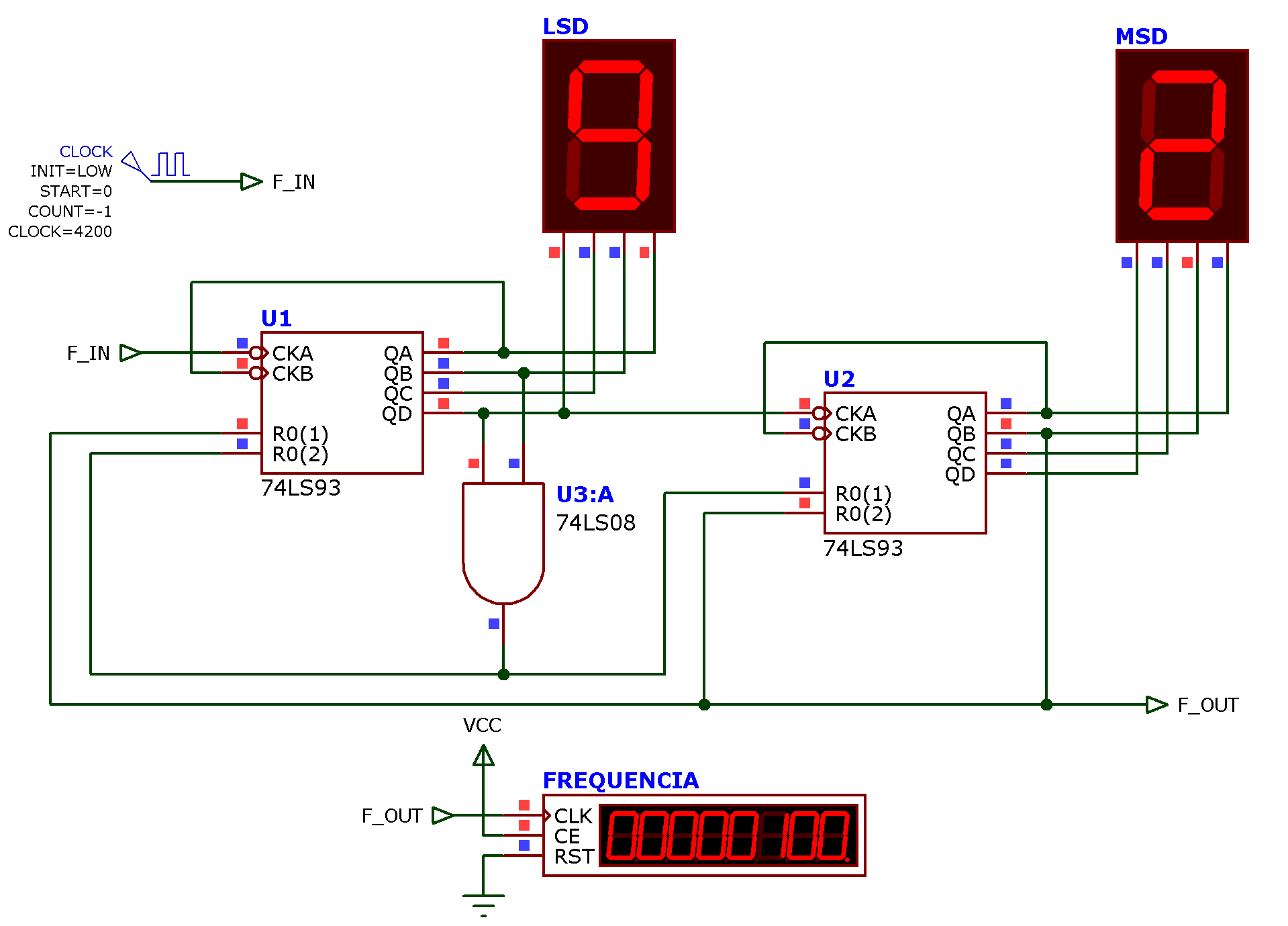

Opção b) Usando CI 7493

Etapa 1: Circuito ÷ 16 cascateado com outro circuito ÷ 16 ==> Total: ÷ 256

Etapa 2: Programar um "Master Reset" quando contagem atinge

Circuito final: contador_div42_74LS93.DSN

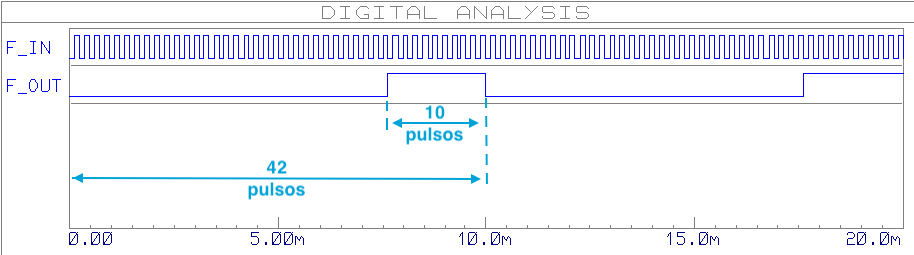

Deduzindo duty-cycle do circuito acima:

Parte da Tabela verdade do contador:

xxxxxxxxxxSaídas U2: | Saídas U1: | ResultadoQ3 Q2 Q1 Q0 | Q3 Q2 Q1 Q0 | Contagem-----------------+------------------+--------------------0 0 0 0 | 0 0 0 0 | 00 0 0 0 | 0 0 0 1 | 1: | : | :0 0 0 1 | 1 1 1 1 | 1F_(16)=31_(10)0 0 1 0 | 0 0 0 0 | 20_(16)=32_(10): | : | :0 0 1 0 | 1 0 0 0 | 28_(16)=40_(10)0 0 1 0 | 1 0 0 1 | 29_(16)=41_(10)0/0 0/0 1/0 0/0 | 1/0 0/0 1/0 0/0 | 2A/0 - Instante do recycle [2A_(16)=42_(10)]

Note:

Repare que

Também é possível usar a ferramenta "Graphs/Digital" para mostrar na tela um diagrama de formas de onda e confirmar visualmente o duty-cycle gerado na saída

Note na figura acima, que a janela de tempo de simulação foi alterada para mostrar os primeiros 20 ns de funcionamento do circuito, com

Opção c) 42 divisível por 6 --> 42/6 = 7 ---> ÷ 42 = ÷ 6, ÷ 7; (circuito não apresentado aqui)

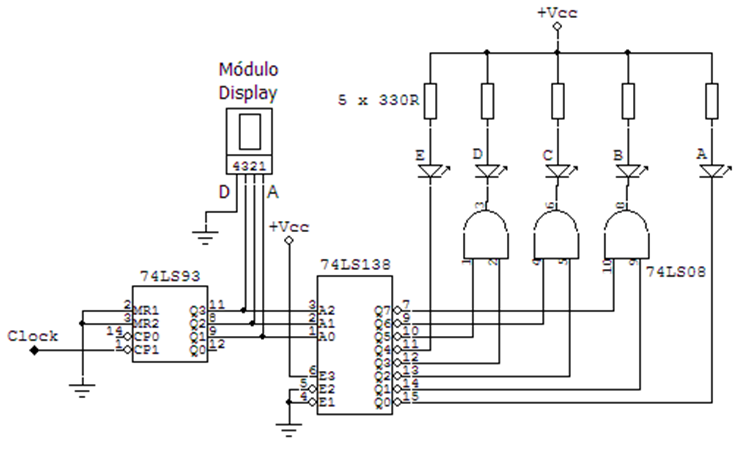

Slide 44: analisando/entendendo o efeito visual produzido pelo circuito.

Circuito:

Levanta-se equações:

Monta-se tabela verdade do circuito:

xxxxxxxxxxNo Pulso | Contad | Led'sClock | Q3Q2Q1 | E D C B A---------+--------+-----------0. | 0 0 0 | X1 | 0 0 1 | X2. | 0 1 0 | X3. | 0 1 1 | X4. | 1 0 0 | X5. | 1 0 1 | X6. | 1 1 0 | X7. | 1 1 1 | X8. | 0 0 0 | X9. | 0 0 1 | X

Obs: Led "X" significa Led ativado.

Conclusão: este circuito gera um efeito visual de "vai-e-vêm" sobre 5 leds.

Prof. Fernando Passold, em 10/09/2021.