Projeto Contador Síncrono 2021/2

Projeto deste semestre:

Como resolver?

1) Quantos FF's?

Solução:

Considerações iniciais: o contador proposto possui 6 estados. 6 estados => 3 FF's. 3 FF's. permitem

As combinações binárias ou estados que não são atingidas pelo circuto usando os 3 FF's, são os estados: 0 e 5.

2) Como continuar?

Solução: Levantar tabela de transição.

A tabela de transição relaciona como o contador parte de certo estado atual,

Em resumo esta tabela (de transição) é necessária para que possamos estabelecer a forma como devem ser ajustadas as entradas de cada FF adotado (no caso, FF's D) para que o circuito realize cada uma das transições (de estado) desejadas:

Num primeiro momento, a tabela de transição fica igual com a representada abaixo:

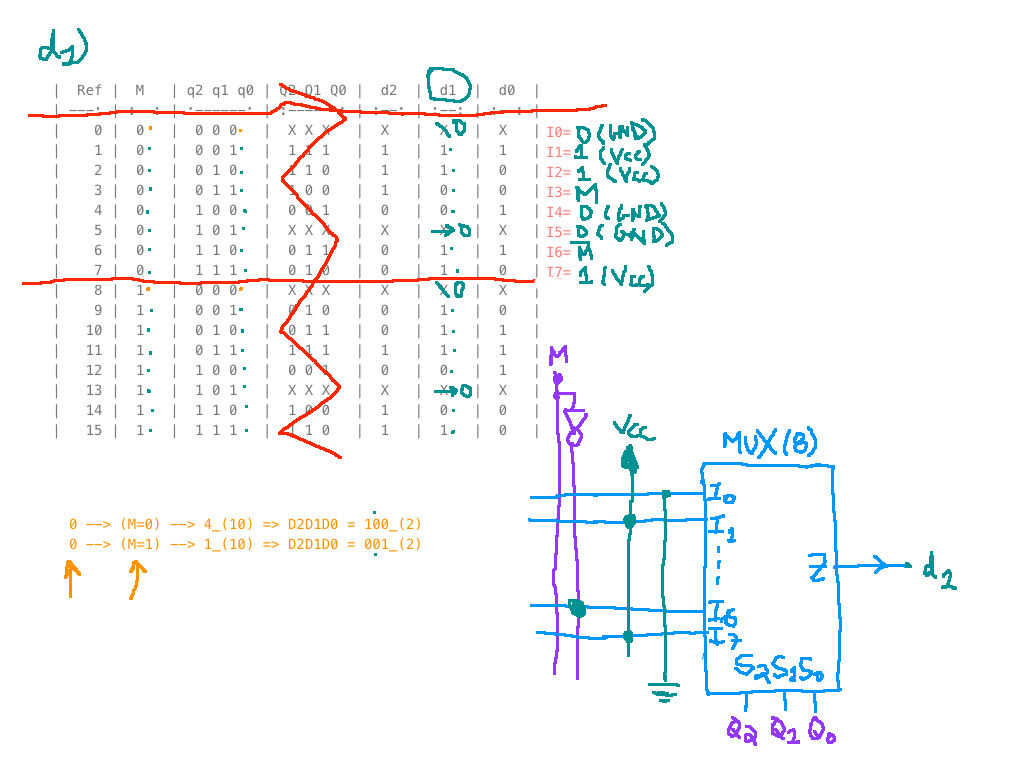

| Ref | M | q2 q1 q0 | Q2 Q1 Q0 | d2 | d1 | d0 |

|---|---|---|---|---|---|---|

| 0 | 0 | 0 0 0 | X X X | X | X | X |

| 1 | 0 | 0 0 1 | 1 1 1 | |||

| 2 | 0 | 0 1 0 | 1 1 0 | |||

| 3 | 0 | 0 1 1 | 1 0 0 | |||

| 4 | 0 | 1 0 0 | 0 0 1 | |||

| 5 | 0 | 1 0 1 | X X X | X | X | X |

| 6 | 0 | 1 1 0 | 0 1 1 | |||

| 7 | 0 | 1 1 1 | 0 1 0 | |||

| 8 | 1 | 0 0 0 | X X X | X | X | X |

| 9 | 1 | 0 0 1 | 0 1 0 | |||

| 10 | 1 | 0 1 0 | 0 1 1 | |||

| 11 | 1 | 0 1 1 | 1 1 1 | |||

| 12 | 1 | 1 0 0 | 0 0 1 | |||

| 13 | 1 | 1 0 1 | X X X | X | X | X |

| 14 | 1 | 1 1 0 | 1 0 0 | |||

| 15 | 1 | 1 1 1 | 1 1 0 |

Terminando/completando a tabela:

Considerando a tabela de transição do FF adotado teremos:

Nota-se que para "programar" o FF-D, basta simplesmente "copiar" na entrada

Completando então a Tabela de transição do circuito:

| Ref | M | q2 q1 q0 | Q2 Q1 Q0 | d2 | d1 | d0 |

|---|---|---|---|---|---|---|

| 0 | 0 | 0 0 0 | X X X | X | X | X |

| 1 | 0 | 0 0 1 | 1 1 1 | 1 | 1 | 1 |

| 2 | 0 | 0 1 0 | 1 1 0 | 1 | 1 | 0 |

| 3 | 0 | 0 1 1 | 1 0 0 | 1 | 0 | 0 |

| 4 | 0 | 1 0 0 | 0 0 1 | 0 | 0 | 1 |

| 5 | 0 | 1 0 1 | X X X | X | X | X |

| 6 | 0 | 1 1 0 | 0 1 1 | 0 | 1 | 1 |

| 7 | 0 | 1 1 1 | 0 1 0 | 0 | 1 | 0 |

| 8 | 1 | 0 0 0 | X X X | X | X | X |

| 9 | 1 | 0 0 1 | 0 1 0 | 0 | 1 | 0 |

| 10 | 1 | 0 1 0 | 0 1 1 | 0 | 1 | 1 |

| 11 | 1 | 0 1 1 | 1 1 1 | 1 | 1 | 1 |

| 12 | 1 | 1 0 0 | 0 0 1 | 0 | 0 | 1 |

| 13 | 1 | 1 0 1 | X X X | X | X | X |

| 14 | 1 | 1 1 0 | 1 0 0 | 1 | 0 | 0 |

| 15 | 1 | 1 1 1 | 1 1 0 | 1 | 1 | 0 |

Lembrando que qualquer linha incorreta relacionada acima, vai levar a um comportamento incorredo do circuito.

Continuando...

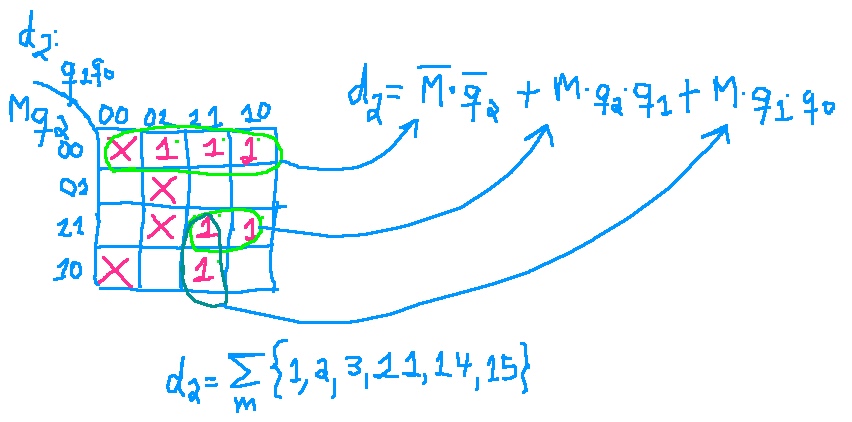

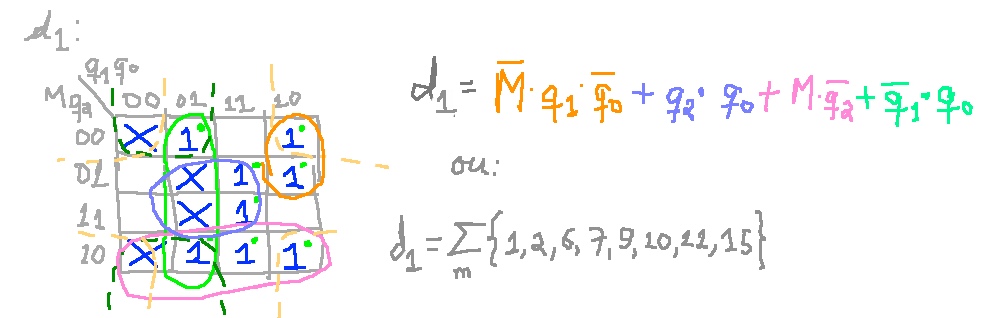

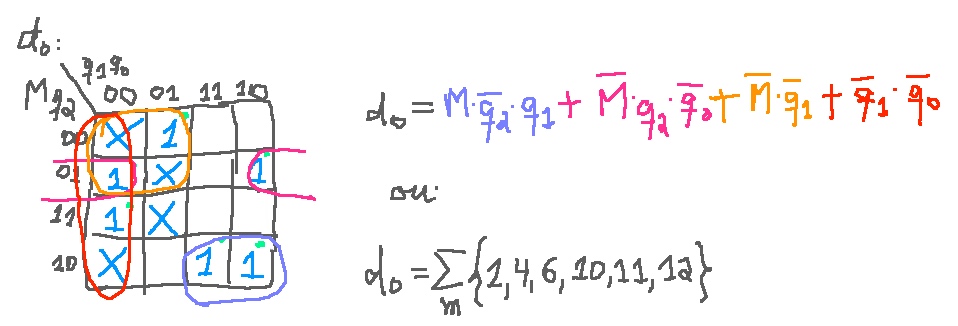

3) Levantando as equações para as entradas de controle dos FFs adotados:

Através de Mapas de Karnaugh para cada um dos FF's:

Esta solução, baseada em Mapas de Karnaugh, pressupõe que serão usadas portas lógicas básicas. Isto leva a um total de:

- portas AND(3) x 5

- portas AND(2) x 6

- portas OR(3) x 1

- portas OR(4) x 2

Total somente para a parte de comando dos FF's: 6 x CI's + CI para os 3 x FF's D (com saída

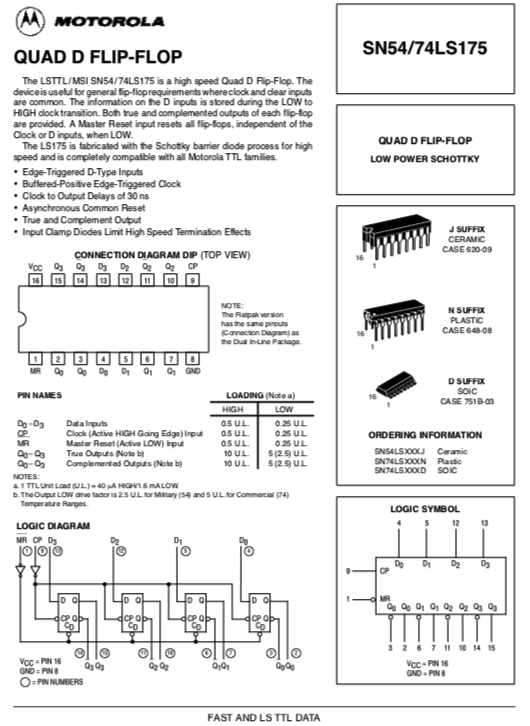

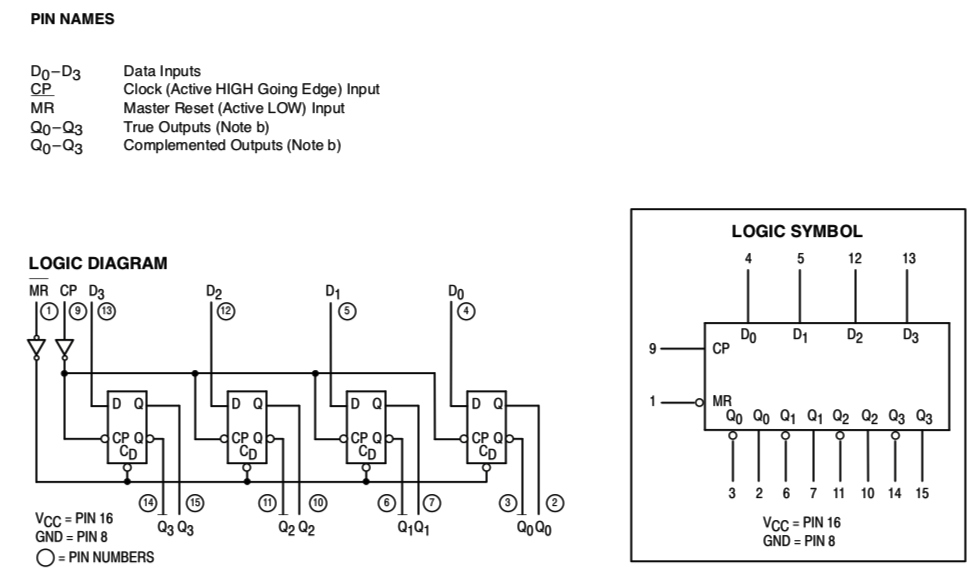

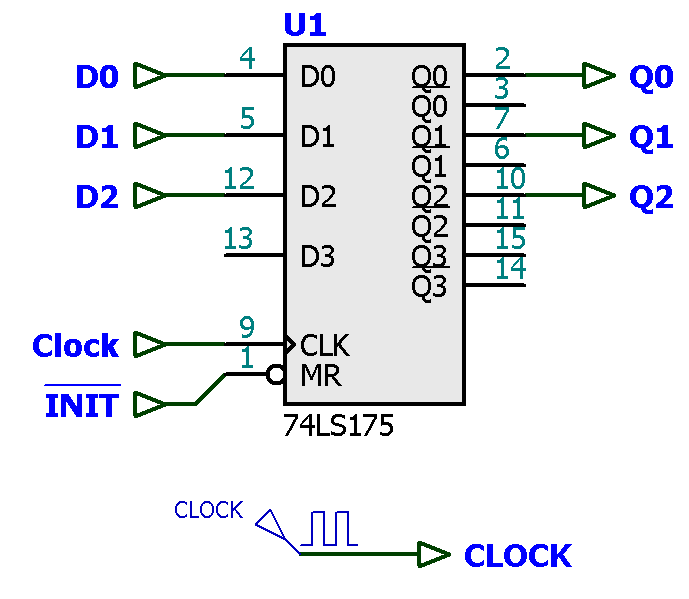

Lembrando que queremos usar o CI 74LS175 (Quad FF type D), à exemplo do que já foi usado em semestre anterior, para outro contador síncrono "diferente", ver: https://fpassold.github.io/Digitais_2/2020_1/projeto_contador_sincrono_2020_1.html:

Segue o Datasheet da Motorola para 74LS175:

Revela:

4) Mais considerações para o projeto...

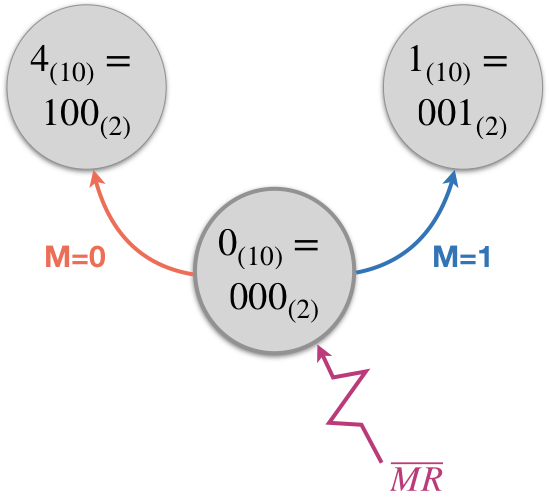

Podemos usar a pastilha 74LS175, mas... existe um porém, se esta pastilha for usada, só conseguimos inicializar o circuito no estado:

Supondo que ativamos o "Master Reset" do 74LS175 quando o circuto é recém alimentado fazendo uso de um circuito RC, somos obrigados à analizar os Mapas de Karnaugh anteriores para prever como o circuito se comportará quando colocado no estado inicial "0".

A questão é:

- O circuito depois de inicializado em "0", converge para algum estado previsto para sua sequência normal de operação (e isto ainda depende do nível lógico da variável

Então somos obrigados à prever como o circuito se comporta quando for inicializado no estado "0".

As situações à serem verificadas são as seguintes:

Então, analizando os Mapas de Karnaugh e agrupamentos realizados para cada entrada dos FF's, temos:

Quando

Note que no Mapa K para

Quando

Notamos que o "5" também não faz parte da sequencia prevista para a contagem, então nossa análise deve prosseguir:

- Quando

- Quando

- Quando

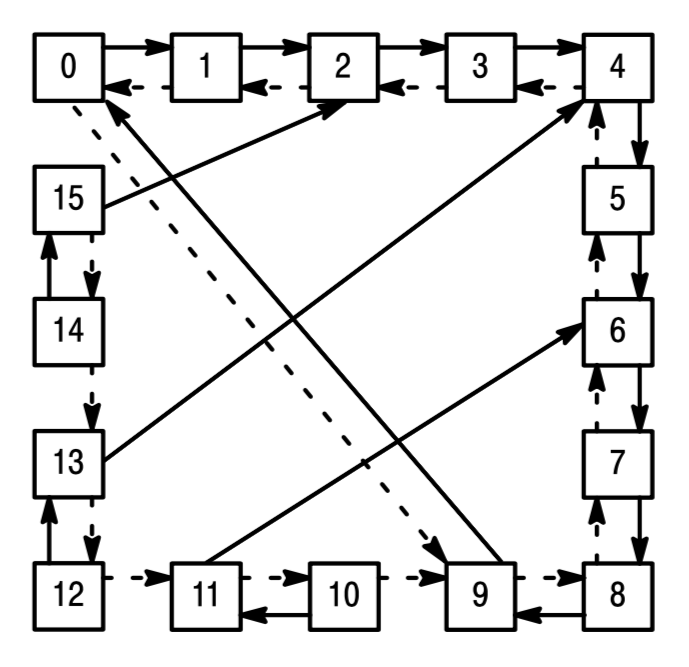

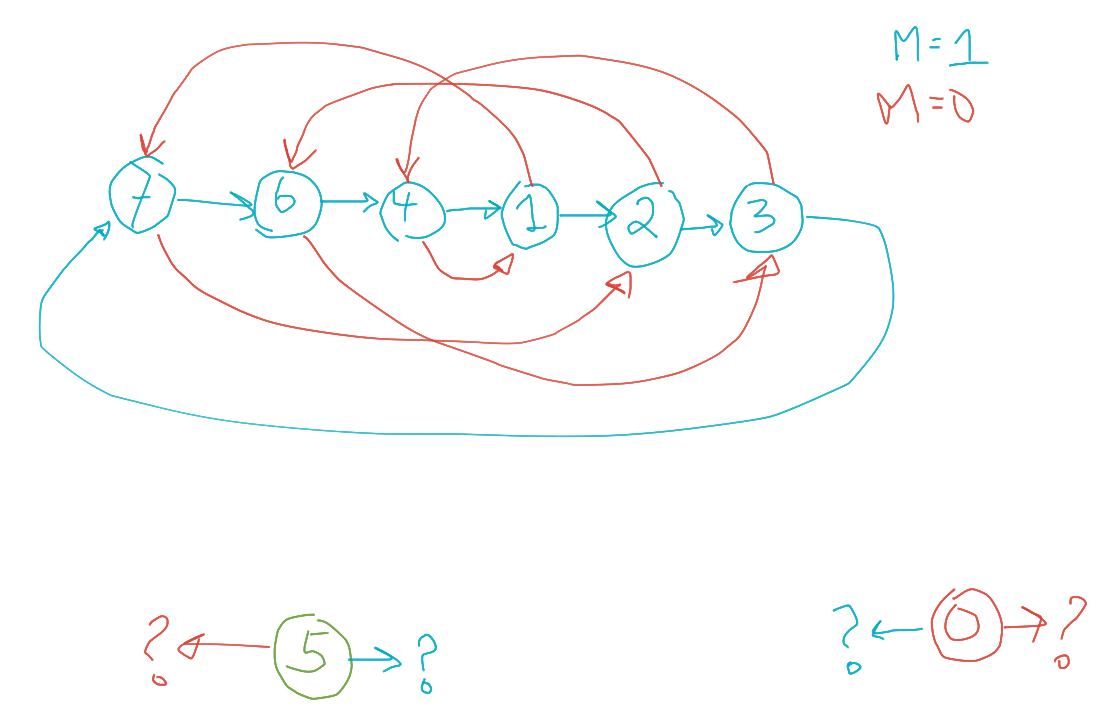

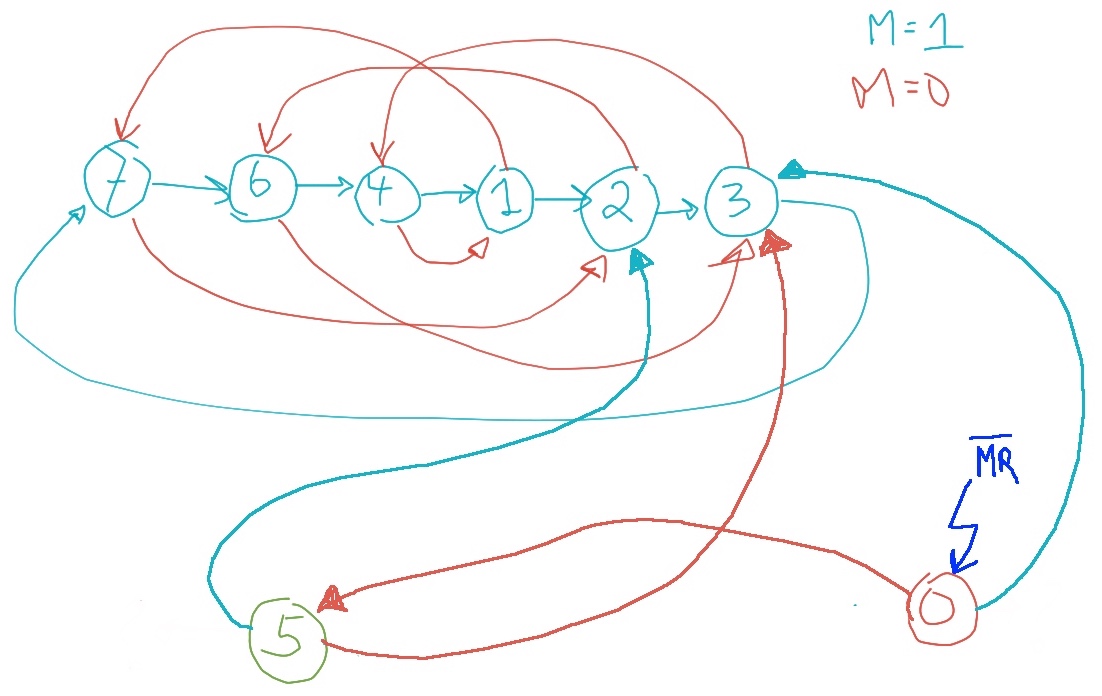

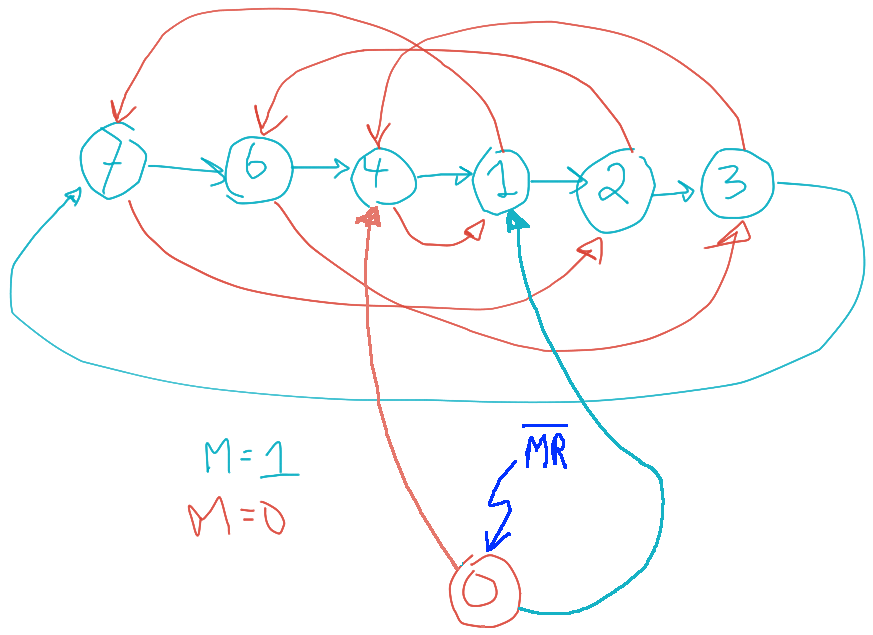

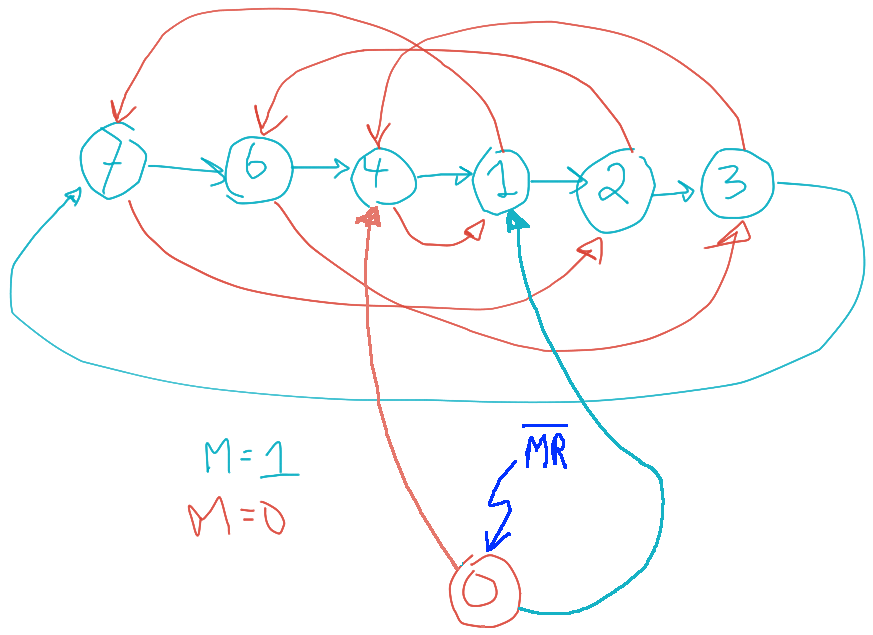

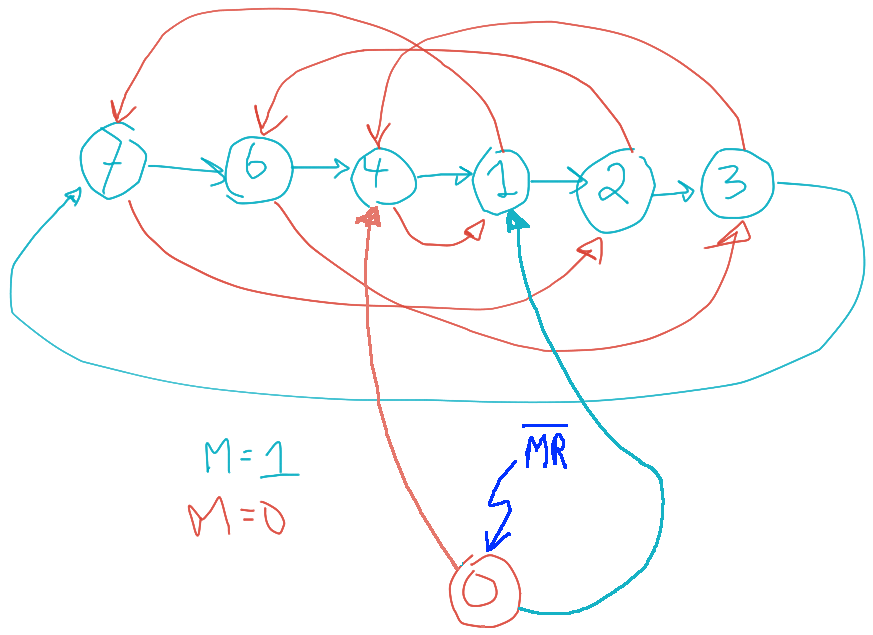

Podemos resumir todo este comportamento num diagrama de estados final:

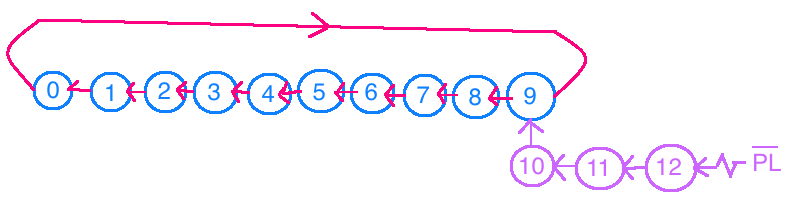

Note que esta sequencia incomum caso o circuito seja inicializado em "0" também ocorre com a pastilha comercial 74LS190 quando a mesma é inicializada (usado PL = "Parallel Load") com o estado "12" por exemplo:

No caso desta pastilha se foi realizado o "PL" com

, e o mesmo estiver ajustado para contar de maneira crescente, a seguinte sequencia de estados será assumida: E se estiver no modo descrente, esta pastilha vai realizar:

Então o fato de eventualmente o circuito apresentar um comportamento inicial estranho não desabona o projeto. O importante é garantir que se os FF's internos da pastilha 74LS175 forem inicializados com uma borda ascendente de "Master Reset", que o circuito evolua para a sequência de estados esperada.

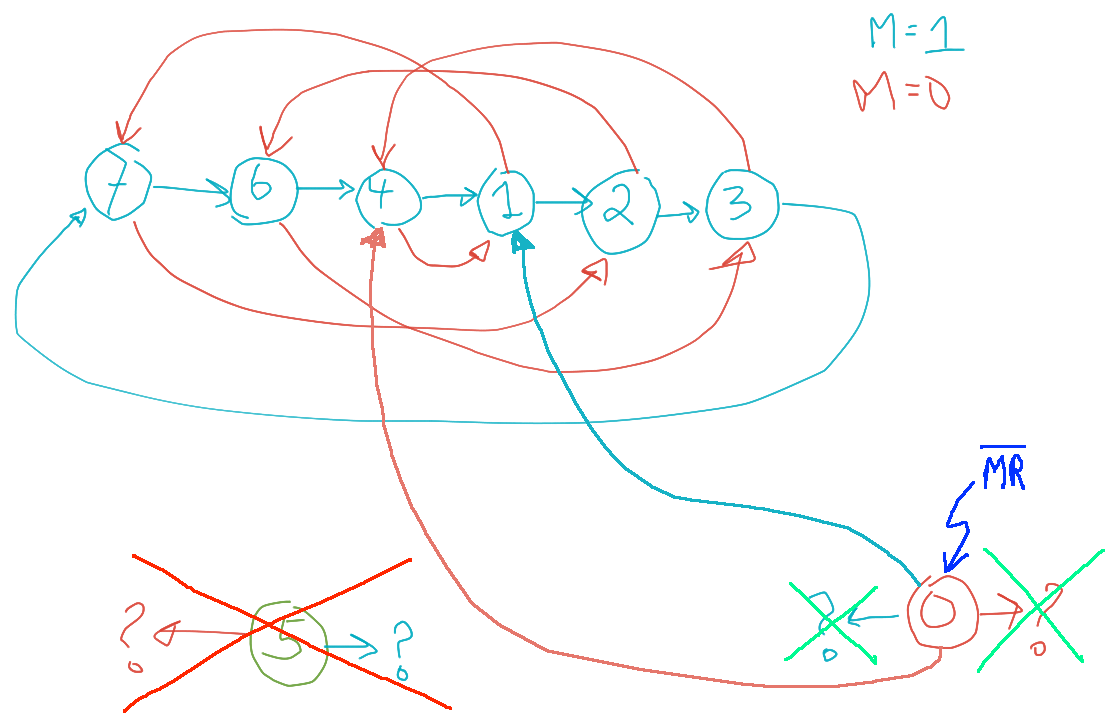

5) Últimas considerações...

Porém... Uma opção que temos para evitar esta inicialização algo confusa e considerando que só podemos iniciar os FF's do nosso circuito no estado "0" (uso do pino de Master Reset da pastilha 74LS175), uma opção mais interessante e possível já que estamos realizando o projeto, é definir explicitamente quais os próximos estados desejados para o nosso circuito depois que os FF's iniciam todos resetados.

Ou seja, ao invés de deixar a "própia sorte", poderíamos "forçar" as transições iniciais e realizar algo como:

Ou seja, significa que queremos agora fazer (diagrama de estados final):

Isto significa que temos que alterar algumas linhas na nossa tabela de transição do circuito para "forçar" estas transições iniciais...

Até aqui em 08/10/2021.

Continuando o projeto em 15/10/2021.

Considerando como podemos implementar o circuito de comando dos FF's...

Ao invés de gastar 6 CI's apenas com portas lógicas básicas necessárias para propiciar o comando desejado aos FF's-D, poderíamos implementar as equações necessárias para

A solução usando DEC, implica, usar

- Para

- Para

- Para

Resumindo, além do DEC serão necessárias + 3 pastilhas (AND/NAND) de 8 entradas (existente comercialmente), totalizando uma solução que empregaria:

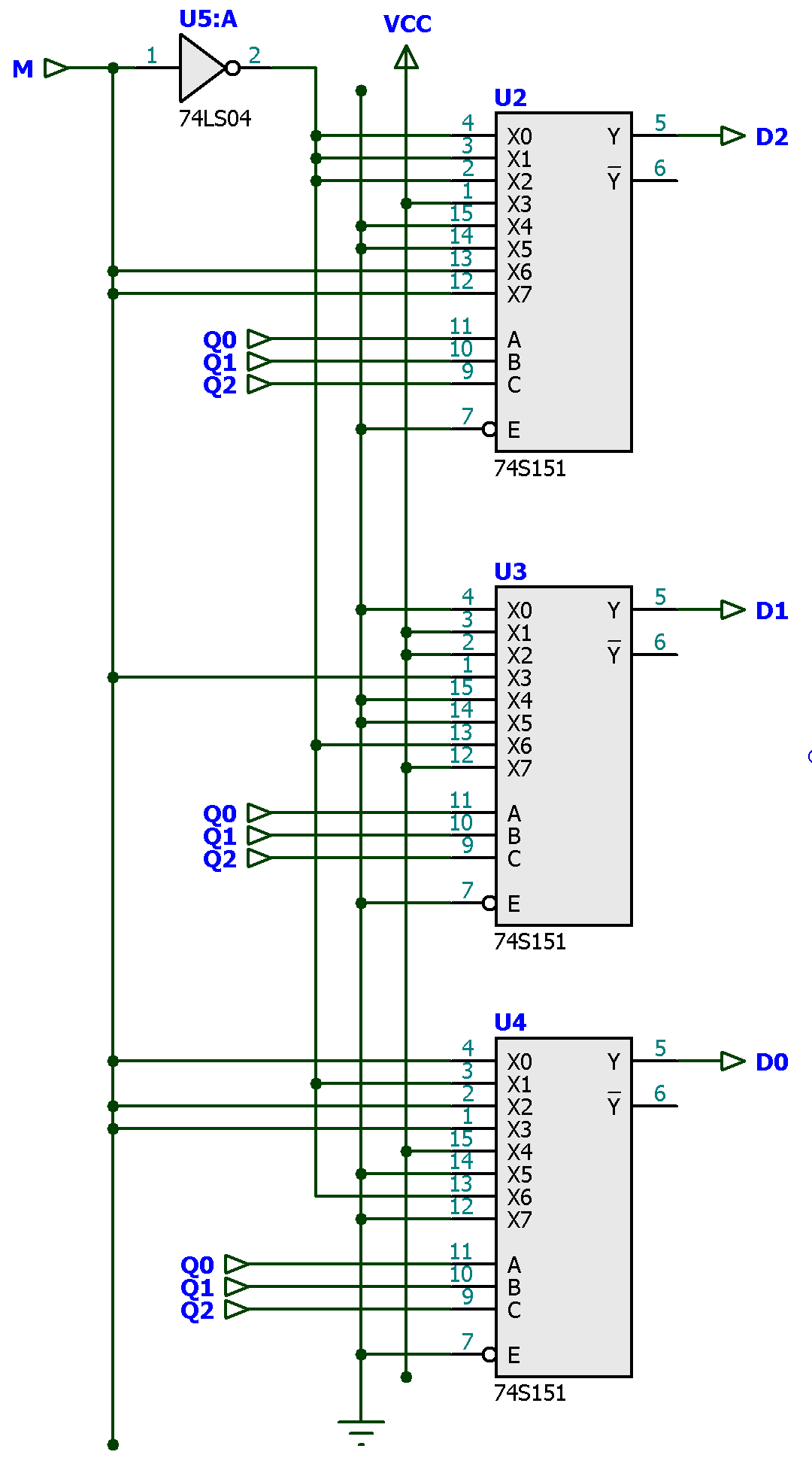

A solução usando MUX exigiria um MUX de 16 canais de saída para cada FF, também uma pastilha "grande" (de 24 pinos). Mas a "programação" destes MUXes também pode ser realizada usando MUXes de 8 canais de saída (pastilhas "tradicionais" de 14 ou 16 pinos). Neste caso, estariámos empregado:

Optando pela solução usando MUXes:

- Opção 1) Usar MUXes de 4 canais de entrada (pastilha de 24 pinos);

- Opção 2) Usar MUXes de 3 canais de entrada (pastilha de 14/16 pinos):

Optando pela opção 2: Usando MUXES de 8 canais de saída.

Programando os MUXes:

Lembrando a "programação" especial desejado para o circuito quando o mesmo inicia com os FF's resetados (circuito inicia com borda ascendente da entrada Master Reset do CI 74LS175):

Programação do MUX(8) para

xxxxxxxxxxS2 S1 S0| Ref | M | q2 q1 q0 | d2 | Entradas (programação) do MUX| 0 | 0 | 0 0 0 | 1(*) | I0=/M --> 0 --> (M=0) --> D2=1| 1 | 0 | 0 0 1 | 1 | I1=/M| 2 | 0 | 0 1 0 | 1 | I2=/M| 3 | 0 | 0 1 1 | 1 | I3=1 (Vcc)| 4 | 0 | 1 0 0 | 0 | I4=0 (GND)| 5 | 0 | 1 0 1 | X | I5=0 (GND) --> Implica em 5 --> 0 (M=X)| 6 | 0 | 1 1 0 | 0 | I6=M| 7 | 0 | 1 1 1 | 0 | I7=M----------------------------------| 8/0 | 1 | 0 0 0 | 0(*) | --> 0 --> (M=1) --> D2=0| 9/1 | 1 | 0 0 1 | 0 || 10/2 | 1 | 0 1 0 | 0 || 11/3 | 1 | 0 1 1 | 1 || 12/4 | 1 | 1 0 0 | 0 || 13/5 | 1 | 1 0 1 | X || 14/6 | 1 | 1 1 0 | 1 || 15/7 | 1 | 1 1 1 | 1 |

Programação do MUX(8) para

Programação do MUX(8) para

xxxxxxxxxx| Ref | M | q2 q1 q0 | Q2 Q1 Q0 | d0 | Programção do MUX-------------------------------------------------| 0 | 0 | 0 0 0 | X X X | 0(*)| I0= M % 0 --> (M=0) --> d0=0| 1 | 0 | 0 0 1 | 1 1 1 | 1 | I1= /M| 2 | 0 | 0 1 0 | 1 1 0 | 0 | I2= M| 3 | 0 | 0 1 1 | 1 0 0 | 0 | I3= M| 4 | 0 | 1 0 0 | 0 0 1 | 1 | I4= 1 (Vcc)| 5 | 0 | 1 0 1 | X X X | X | I5= 0 % 5 --> (M=X) --> d0=0| 6 | 0 | 1 1 0 | 0 1 1 | 1 | I6= /M| 7 | 0 | 1 1 1 | 0 1 0 | 0 | I7= 0 (Vcc)------------------------------------------------| 8/0 | 1 | 0 0 0 | X X X | 1(*)| % 0 --> (M=1) ---> d0=1| 9/1 | 1 | 0 0 1 | 0 1 0 | 0 || 10/2 | 1 | 0 1 0 | 0 1 1 | 1 || 11/3 | 1 | 0 1 1 | 1 1 1 | 1 || 12/4 | 1 | 1 0 0 | 0 0 1 | 1 || 13/5 | 1 | 1 0 1 | X X X | X || 14/6 | 1 | 1 1 0 | 1 0 0 | 0 || 15/7 | 1 | 1 1 1 | 1 1 0 | 0 |

5) Circuito elétrico/lógico final

Parte da pastilha com FF's-D:

Parte da entrada

Parte dos MUXes (programação dos comandos dos FF's):

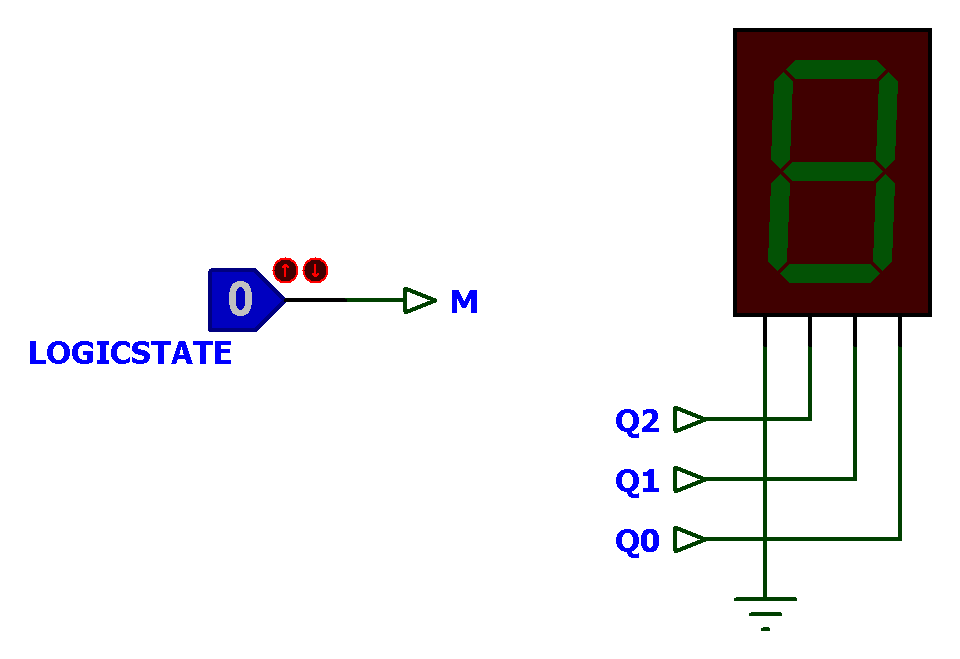

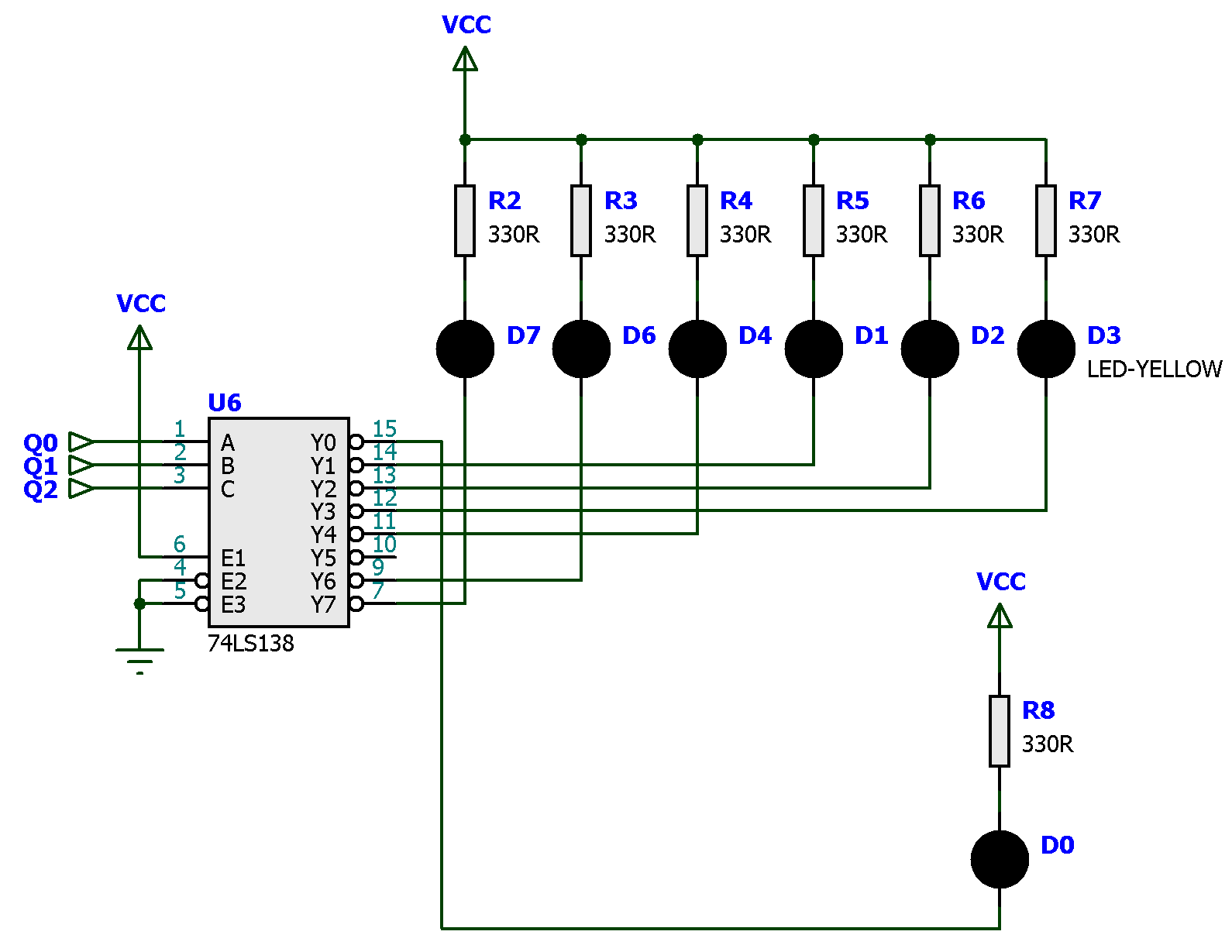

Parte extra (opcional) que organiza um "painel mímico" que visa imitar o digrama de estados proposto para este contador:

Alimentação dos CIs:

| CI | 74LS175 | 74LS151 | 74LS04 | 74LS138 |

|---|---|---|---|---|

| Vcc: | Pin 16 | Pin 16 | Pin 14 | Pin 16 |

| GND: | Pin 8 | Pin 8 | Pin 7 | Pin 8 |

6) Simulações

As figuras à seguir mostram o diagrama de estados desejado o resultado simulado do circuito:

Simulação iniciando circuito com

| Simulação | Diagrama Estados |

|---|---|

|  |

Simulação iniciando circuito com

| Simulação | Diagrama Estados |

|---|---|

|  |

Simulação variando

| Simulação | Diagrama de Estados |

|---|---|

|  |

Lista de Material:

- U1: 1 x CI 74LS175 (Quad FF D,

- U2, U3, U4: 3 x CIs 74LS151 (MUX-8);

- U5: 1 x 74LS04 (6 x NOT);

- U6: 1 x 74LS138 (DEC 3/8);

- D0, D1, D2, D3, D4, D6, D7: 7x Leds mini-vermelhos alto-contraste;

- R2, R3, R4, R5, R6, R6, R8: 7 x Resistores de 330

- 1 módulo-display 7-segmentos;

- Fonte de alimentação;

- Gerador de sinais.

Prof. Fernando Passold, em 15.10.2021.