### Biestáveis

Circuitos Digitais II Prof. Fernando Passold

### Biestáveis

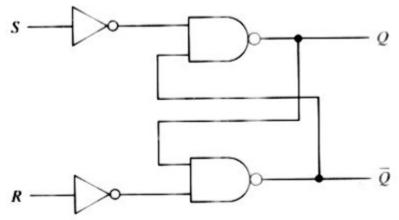

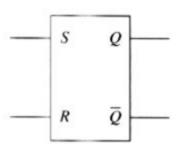

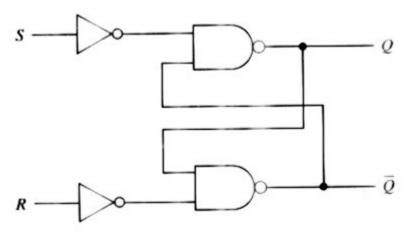

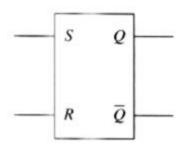

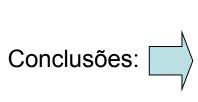

### Biestável RS básico:

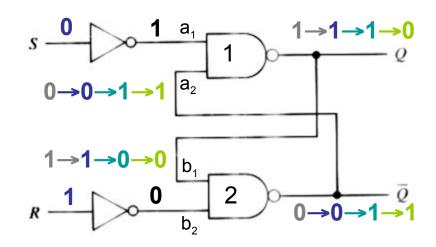

a) Circuito interno com portas NOT e NAND.

b) Símbolo do Biestável RS.

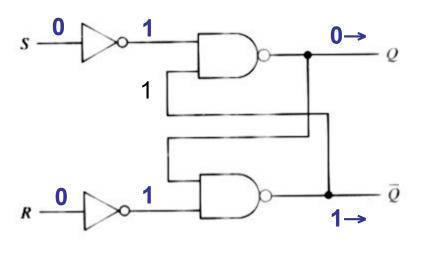

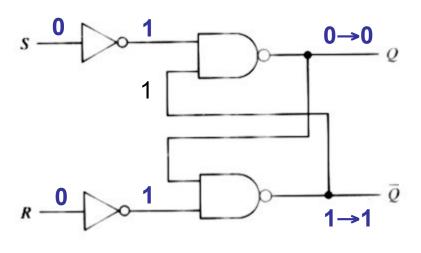

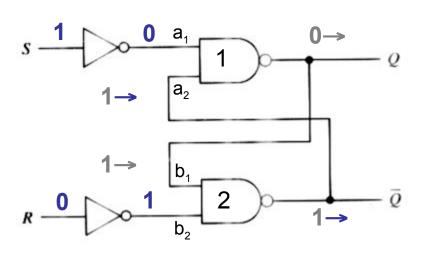

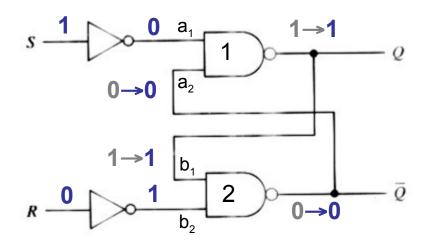

### Condições de "repouso" (mantendo estado):

Condições iniciais: Próximo estado?

$$S=0$$

Q(t)=0  $\longrightarrow$  Q(t+1)=?

(a)

| Α | В | AND | NAND |

|---|---|-----|------|

| 0 | 0 | 0   | 1    |

| 0 | 1 | 0   | 1    |

| 1 | 0 | 0   | 1    |

| 1 | 1 | 1   | 0    |

#### Condições de "repouso" (mantendo estado):

Condições iniciais: Próximo estado?

$$S=0$$

Q(t)=0  $\longrightarrow$  Q(t+1)=?

(a)

| Α | В | AND | NAND |

|---|---|-----|------|

| 0 | 0 | 0   | 1    |

| 0 | 1 | 0   | 1    |

| 1 | 0 | 0   | 1    |

| 1 | 1 | 1   | 0    |

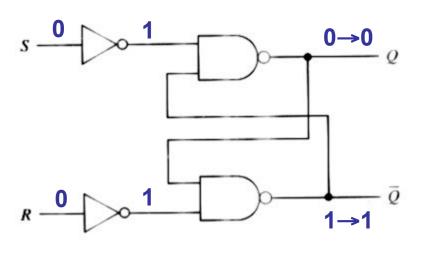

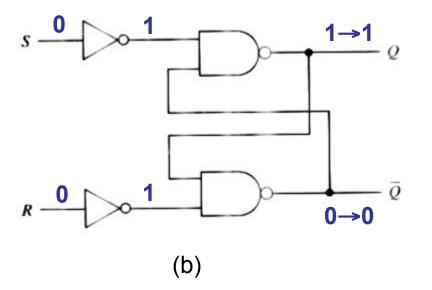

### Condições de "repouso" (mantendo estado):

Condições iniciais:

Próximo estado?

$$S=0$$

Q(t)=0  $\longrightarrow$  Q(t+1)=?

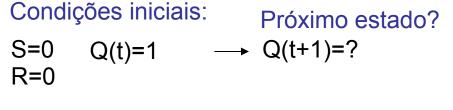

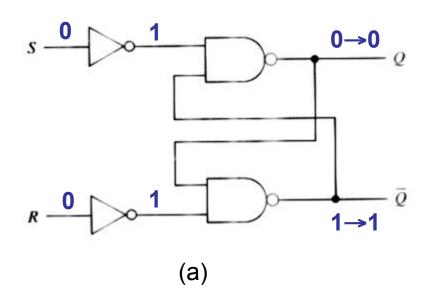

Condições iniciais: Próximo estado? S=0  $Q(t)=1 \longrightarrow Q(t+1)=?$ R=0

(a)

| Α | В | AND | NAND |

|---|---|-----|------|

| 0 | 0 | 0   | 1    |

| 0 | 1 | 0   | 1    |

| 1 | 0 | 0   | 1    |

| 1 | 1 | 1   | 0    |

(b)

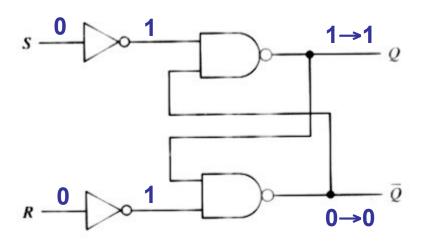

### Condições de "repouso" (mantendo estado):

Condições iniciais:

Próximo estado?

$$S=0$$

$Q(t)=0$   $\longrightarrow$   $Q(t+1)=$

Conclusões:

| Set | Reset | Q(t+1) | Obs:                        |

|-----|-------|--------|-----------------------------|

| 0   | 0     | Q(t)   | Mantêm estado.<br>Não muda. |

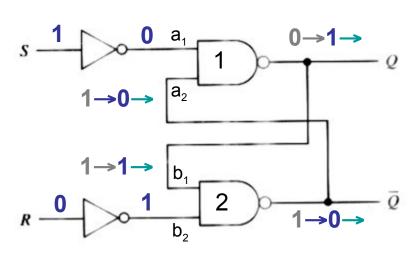

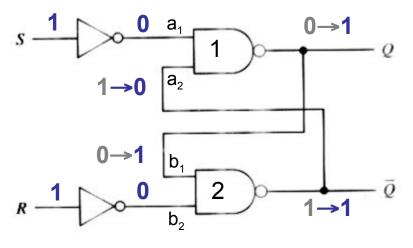

#### **Setando** o biestável:

Condições iniciais:

$$S=1 \qquad Q(t)=0 \qquad \longrightarrow \qquad Q(t+1)=?$$

Diagrama no tempo:

|                | _        |   |  |

|----------------|----------|---|--|

|                |          |   |  |

| S              | $\times$ | 1 |  |

| R              |          | 0 |  |

| a <sub>1</sub> | $\times$ | 0 |  |

| $a_2$          | $\sim$   | 1 |  |

| b₁             | $\times$ | 0 |  |

| $b_2$          | $\times$ | 1 |  |

| Q              |          | 0 |  |

| Q              |          | 1 |  |

| •              |          |   |  |

(a)

Obs: análise supondo que porta 1 é mais rápida que a porta 2.

| Α | В | AND | NAND |

|---|---|-----|------|

| 0 | 0 | 0   | 1    |

| 0 | 1 | 0   | 1    |

| 1 | 0 | 0   | 1    |

| 1 | 1 | 1   | 0    |

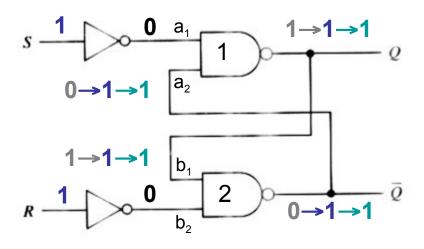

#### **Setando** o biestável:

#### Condições iniciais:

Próximo estado?

S=1 Q(t)=0

$$\longrightarrow$$

Q(t+1)=?

Diagrama no tempo:

|                | 9          |   |     | τορ.σ.       |  |

|----------------|------------|---|-----|--------------|--|

|                |            |   |     |              |  |

| S              | >>         | 1 |     |              |  |

|                |            | 0 |     |              |  |

| a <sub>1</sub> |            | 0 | 0   |              |  |

| $a_2$          |            | 1 | 1   |              |  |

| $b_1$          |            | 0 | 1   | <u> </u><br> |  |

| $b_2$          | $\searrow$ | 1 | 1   | <b>-</b>     |  |

| Q              |            | 0 | 1   |              |  |

| 0              |            | 1 | 1   | _            |  |

| 7              |            |   | : : |              |  |

(a)

Obs: análise supondo que porta 1 é mais rápida que a porta 2.

| Α | В | AND | NAND |

|---|---|-----|------|

| 0 | 0 | 0   | 1    |

| 0 | 1 | 0   | 1    |

| 1 | 0 | 0   | 1    |

| 1 | 1 | 1   | 0    |

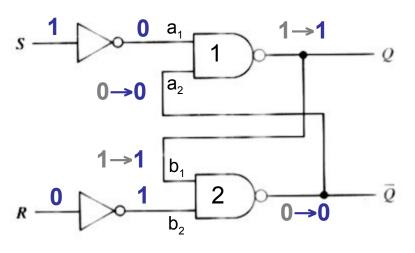

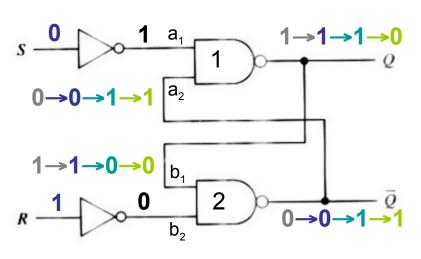

#### **Setando** o biestável:

Condições iniciais:

Próximo estado?

S=1

$$Q(t)=0$$

$\longrightarrow$   $Q(t+1)=?$  R=0

Diagrama no tempo:

|                      | J -         | _ |   |   |  |

|----------------------|-------------|---|---|---|--|

| S                    | $\geq$      | 1 |   |   |  |

| R.                   | $\searrow$  | 0 |   |   |  |

| $a_1$                | $\geq$      | 0 | 0 | 0 |  |

| $\mathbf{a}_2$       | $\geq$      | 1 | 1 | 0 |  |

| $b_1$                | $\times$    | 0 | 1 | 1 |  |

| $b_2$                | $\boxtimes$ | 1 | 1 | 1 |  |

| $\mathbf{Q}$         |             | 0 | 1 | 1 |  |

| $\overline{\hat{0}}$ |             | 1 | 1 | 0 |  |

| Υ.                   |             |   |   |   |  |

(a)

Obs: análise supondo que porta 1 é mais rápida que a porta 2.

| Α | В | AND | NAND |

|---|---|-----|------|

| 0 | 0 | 0   | 1    |

| 0 | 1 | 0   | 1    |

| 1 | 0 | 0   | 1    |

| 1 | 1 | 1   | 0    |

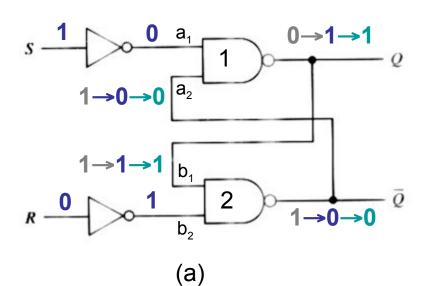

#### **Setando** o biestável:

Condições iniciais:

Próximo estado?

$$S=1 \qquad Q(t)=1 \qquad \longrightarrow Q(t+1)=?$$

$$R=0$$

Diagrama no tempo:

|                                     |             | 1 | •        | • | • |

|-------------------------------------|-------------|---|----------|---|---|

| S                                   | $\boxtimes$ | 1 |          |   |   |

| R                                   | $\searrow$  | 0 |          |   |   |

| a₁                                  | $\times$    | 0 | 0        |   |   |

| $\mathbf{a}_{2}$                    | $\geq$      | 0 | 0        |   |   |

| _                                   |             |   | 1        |   |   |

| $\mathbf{D}_1$                      | $\boxtimes$ | I | <u> </u> |   |   |

| $b_2$                               | $\geq$      | 1 | 1        |   |   |

| Q                                   |             | 1 | 1        |   |   |

| $\stackrel{\underline{\vee}}{\sim}$ |             |   | _        |   |   |

| ()                                  |             | 0 | 0        |   |   |

| 7                                   |             |   |          |   |   |

(b)

Obs: análise supondo que porta 1 é mais rápida que a porta 2.

| Α | В | AND | NAND |

|---|---|-----|------|

| 0 | 0 | 0   | 1    |

| 0 | 1 | 0   | 1    |

| 1 | 0 | 0   | 1    |

| 1 | 1 | 1   | 0    |

#### **Setando** o biestável:

Condições iniciais: Próximo estado? S=1 Q(t)=0  $\rightarrow$  Q(t+1)=? R=0 Condições iniciais: Próximo estado? S=1 Q(t)=1  $\rightarrow$  Q(t+1)=?

Conclusões:

| Set | Reset | Q(t+1) | Obs:           |

|-----|-------|--------|----------------|

| 0   | 0     | Q(t)   | Mantêm estado. |

| 1   | 0     | 1      | Set            |

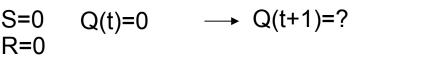

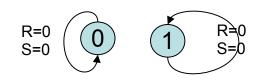

S=0 R=0 S=0 R=0 S=1 R=0

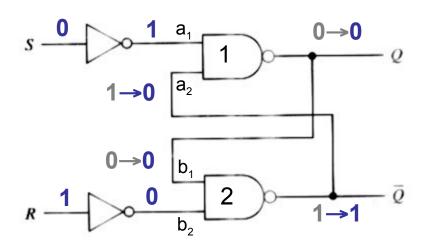

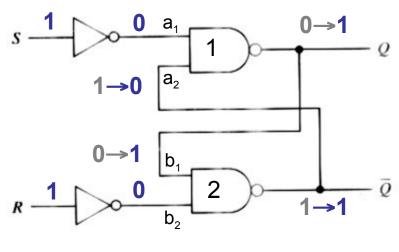

#### Resetando o biestável:

Condições iniciais: Próximo estado?

$$S=0$$

$Q(t)=0$   $\longrightarrow$   $Q(t+1)=?$   $R=1$

(a)

Obs: análise supondo que porta 1 é mais rápida que a porta 2.

| Α | В | AND | NAND |

|---|---|-----|------|

| 0 | 0 | 0   | 1    |

| 0 | 1 | 0   | 1    |

| 1 | 0 | 0   | 1    |

| 1 | 1 | 1   | 0    |

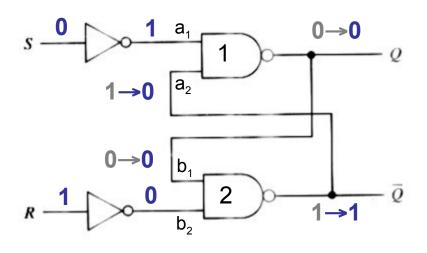

#### Resetando o biestável:

Condições iniciais:

Próximo estado?

$$S=0$$

$Q(t)=1$   $\longrightarrow$   $Q(t+1)=?$   $R=1$

Diagrama no tempo:

|                | _          |   | : |   | • |  |

|----------------|------------|---|---|---|---|--|

| S              | $\geq$     | 0 |   |   |   |  |

| R              | $\sim$     | 1 |   |   |   |  |

| $a_1$          |            | 1 | 1 | 1 | 1 |  |

| $a_2$          |            | 0 | 0 | 1 | 1 |  |

| b₁             | $\geq$     | 1 | 1 | 1 | 0 |  |

| b <sub>2</sub> | $\searrow$ | 0 | 0 | 0 | 0 |  |

| Q              |            | 1 | 1 | 1 | 0 |  |

| 0              |            | 0 | 0 | 1 | 1 |  |

| 7              |            |   |   |   |   |  |

(b)

Obs: análise supondo que porta 1 é mais rápida que a porta 2.

| Α | В | AND | NAND |

|---|---|-----|------|

| 0 | 0 | 0   | 1    |

| 0 | 1 | 0   | 1    |

| 1 | 0 | 0   | 1    |

| 1 | 1 | 1   | 0    |

#### Resetando o biestável:

Condições iniciais:

Próximo estado?

$$S=0$$

Q(t)=0  $\longrightarrow$  Q(t+1)=?

Condições iniciais: Próximo estado? S=0 Q(t)=1  $\longrightarrow$  Q(t+1)=?

(a)

Conclusões:

| Set | Reset | Q(t+1) | Obs:           |

|-----|-------|--------|----------------|

| 0   | 0     | Q(t)   | Mantêm estado. |

| 1   | 0     | 1      | Set            |

| 0   | 1     | 0      | Reset          |

#### Setando e Resetando simultaneamente:

Condições iniciais: Próximo estado?

S=1

$$Q(t)=0$$

$\longrightarrow$   $Q(t+1)=?$  R=1

|    | _ | 1 |

|----|---|---|

| 1  | 2 | ١ |

| 1  | a | ı |

| ١, |   | , |

| Α | В | AND | NAND |

|---|---|-----|------|

| 0 | 0 | 0   | 1    |

| 0 | 1 | 0   | 1    |

| 1 | 0 | 0   | 1    |

| 1 | 1 | 1   | 0    |

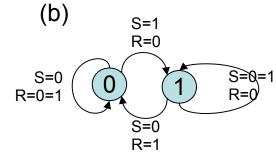

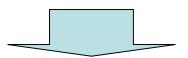

### Biestável básico RS

#### Conclusões finais:

- a) Circuito interno com portas NOT e NAND.

- c) Tabela funcional:

| Set | Reset | Q(t+1) | Obs:                                |

|-----|-------|--------|-------------------------------------|

| 0   | 0     | Q(t)   | Mantêm estado.                      |

| 1   | 0     | 1      | Set                                 |

| 0   | 1     | 0      | Reset                               |

| 1   | 1     | 1      | Não utilizado* ( $Q=\overline{Q}$ ) |

- b) Símbolo do Biestável RS.

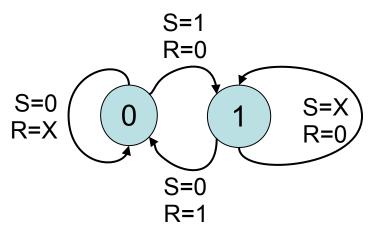

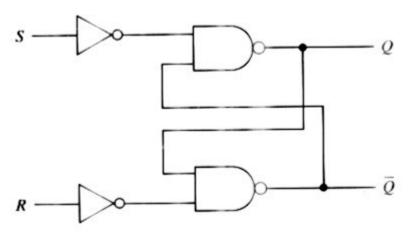

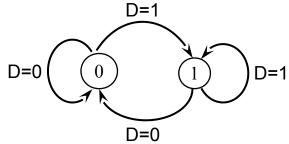

- d) Diagrama de estados:

#### Setando e Resetando simultaneamente:

Próximo estado?

$$\rightarrow$$

Q(t+1)=?

Próximo estado?

S=1

$$Q(t)=1 \longrightarrow Q(t+1)=?$$

R=1

(a)

| Set | Reset | Q(t+1) | Obs:                                       |

|-----|-------|--------|--------------------------------------------|

| 0   | 0     | Q(t)   | Mantêm estado.                             |

| 1   | 0     | 1      | Set                                        |

| 0   | 1     | 0      | Reset                                      |

| 1   | 1     | 1      | Não utilizado* ( <i>Q</i> = <del>Q</del> ) |

S=0 R=0=1 R=X S=0 R=1

### Biestável básico RS

a) Circuito interno com portas NOT e NAND.

#### c) Tabela funcional:

| Set | Reset | Q(t+1) | Obs:                                |

|-----|-------|--------|-------------------------------------|

| 0   | 0     | Q(t)   | Mantêm estado.                      |

| 1   | 0     | 1      | Set                                 |

| 0   | 1     | 0      | Reset                               |

| 1   | 1     | 1      | Não utilizado* ( $Q=\overline{Q}$ ) |

d) Diagrama de estados:

e) Equação de transição:

$$Q(t+1)=S(t)+\overline{R(t)}\cdot Q(t)$$

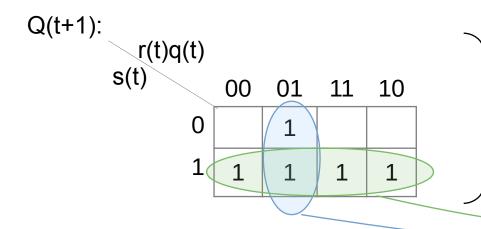

### Biestável básico RS

#### Dedução e. de transição:

| Set | Reset | Q(t+1) | Obs:                                       |

|-----|-------|--------|--------------------------------------------|

| 0   | 0     | Q(t)   | Mantêm estado.                             |

| 1   | 0     | 1      | Set                                        |

| 0   | 1     | 0      | Reset                                      |

| 1   | 1     | 1      | Não utilizar: $Q(t+1) = \overline{Q}(t+1)$ |

d) Diagrama de estados:

e) Equação de transição:

$$Q(t+1)=S(t)+\overline{R(t)}\cdot Q(t)$$

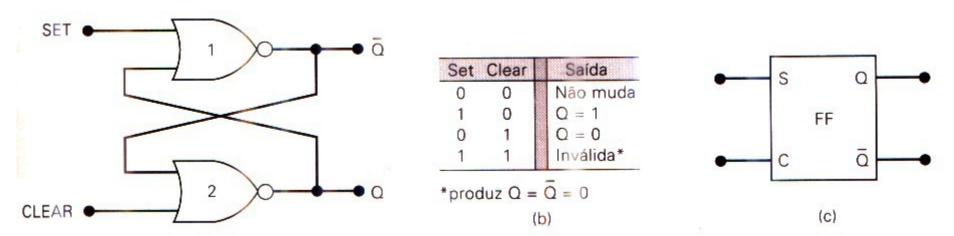

#### Outros biestáveis RS:

Biestável RS básico com portas NOR:

#### Biestável RS com portas NOT+OR:

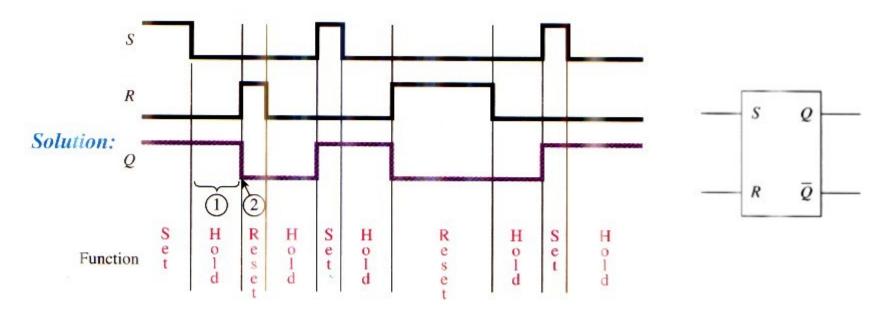

#### Biestável RS:

### Exemplo de uso:

| Set | Reset | Q(t+1) | Obs:              |

|-----|-------|--------|-------------------|

| 0   | 0     | Q(t)   | Mantêm estado.    |

| 1   | 0     | 1      | Set               |

| 0   | 1     | 0      | Reset             |

| 1   | 1     | 1      | Condição inválida |

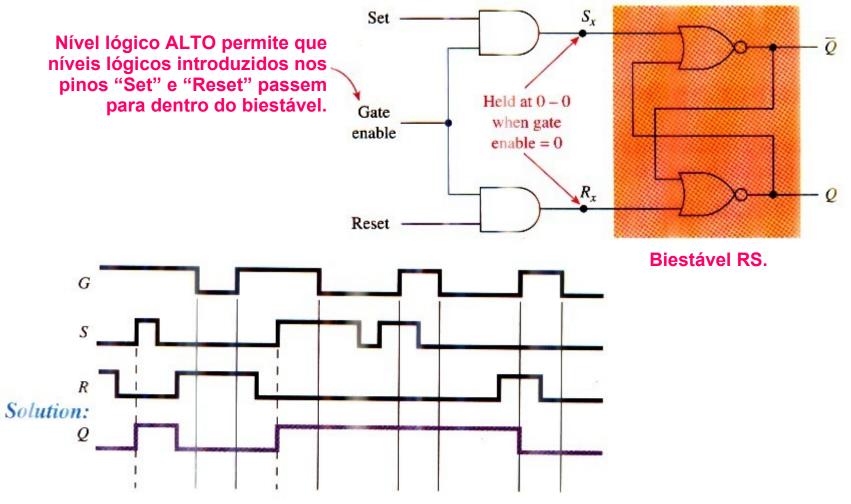

#### Latch RS

#### Biestável com entrada de ENABLE:

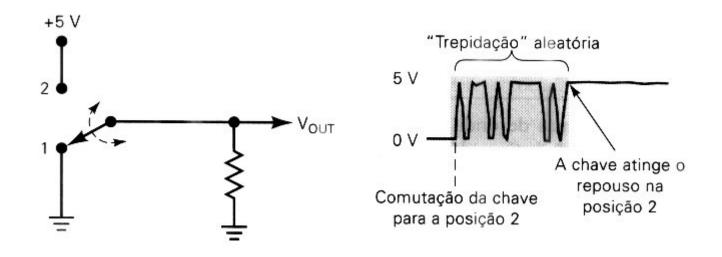

### Aplicação de biestável RS

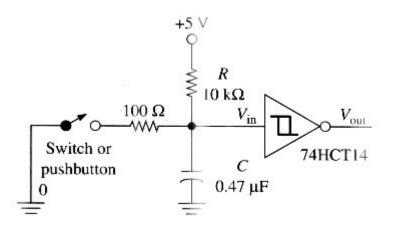

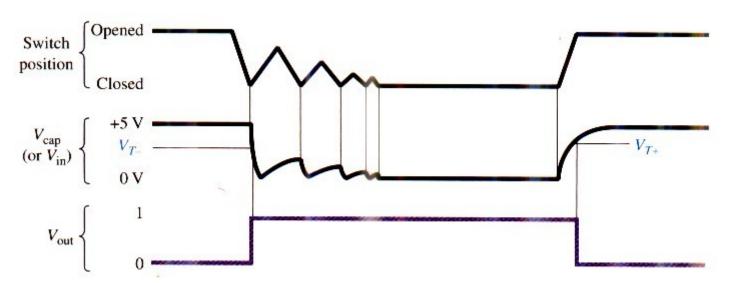

Circuito problema do efeito "bouncing" de chaves:

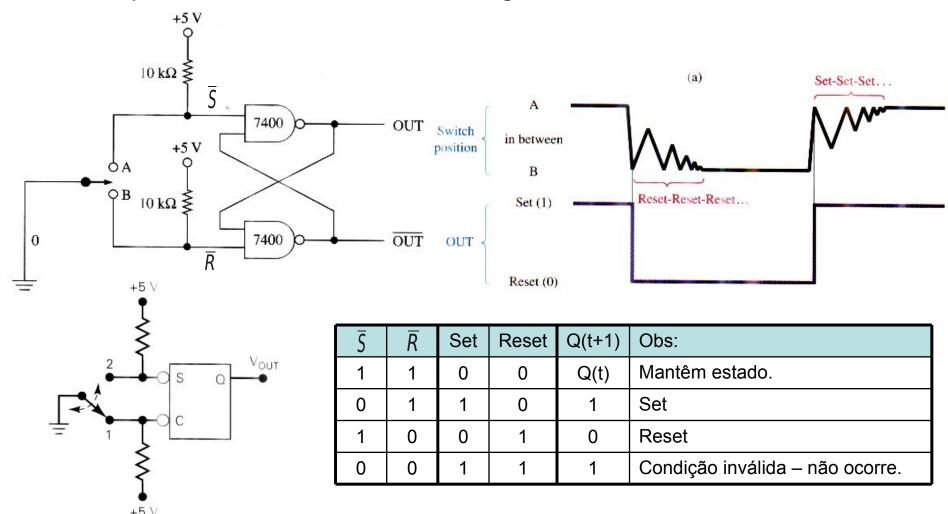

### Aplicação de biestável RS

Circuito para eliminar efeito "bouncing" de chaves:

### Circuitos de Debouncing

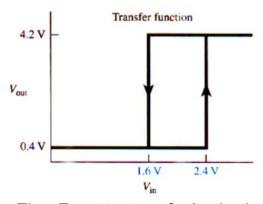

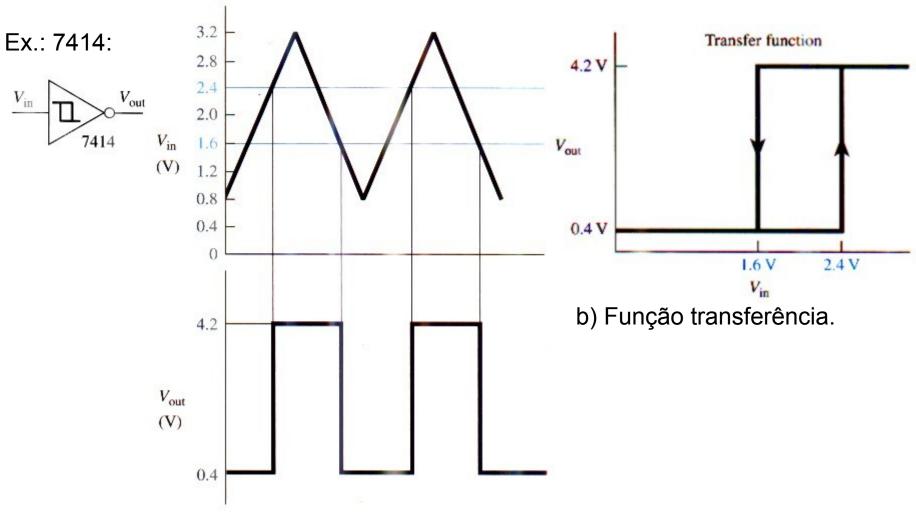

Outro circuito empregando Schmitt-trigger:

Fig.: Função transferência do Schmitt-trigger.

### Operação de um Schmitt trigger:

a) Simulação de Schmitt-trigger.

Biestáveis 11/03/19 <a>⊅ pág 27</a>

## Latches x Flip\_Flops: Biestáveis

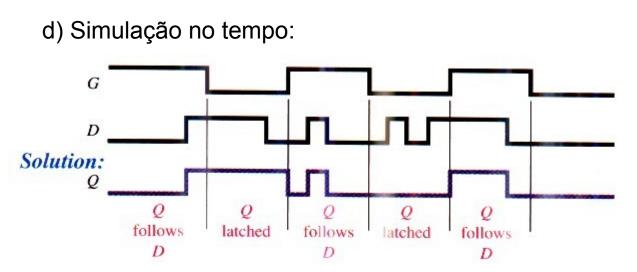

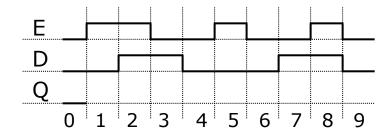

Latch: entrada "extra" (Enable) sensível à nível lógico:

## Latches x Flip\_Flops: Biestáveis

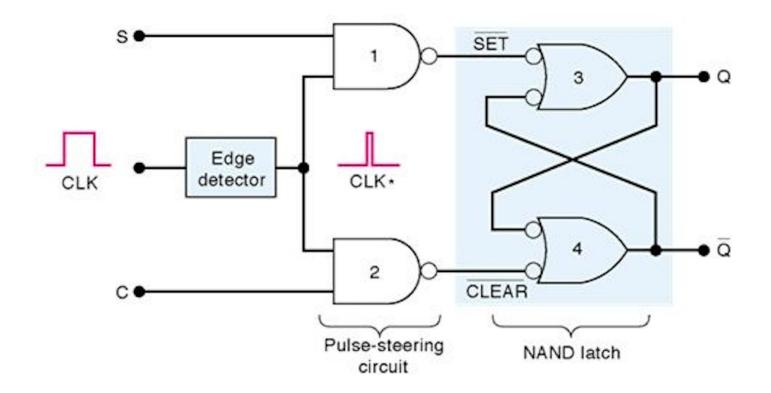

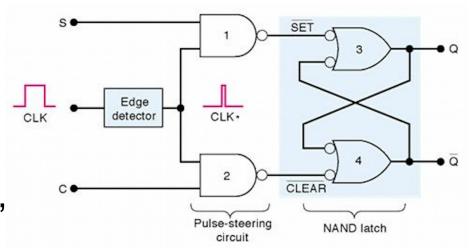

Flip-Flop: entrada "extra" (Clock) sensível à borda do sinal (nesta entrada):

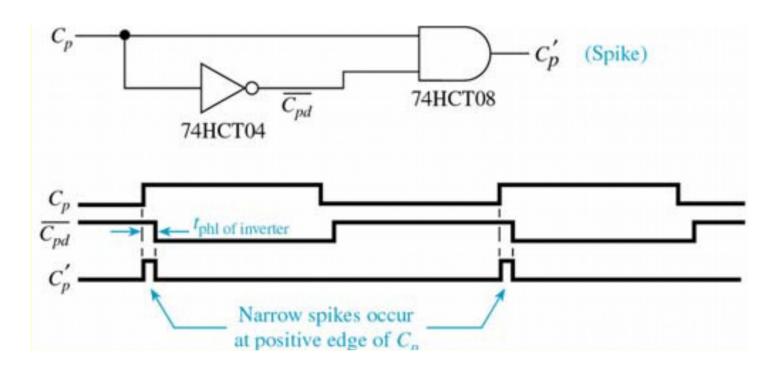

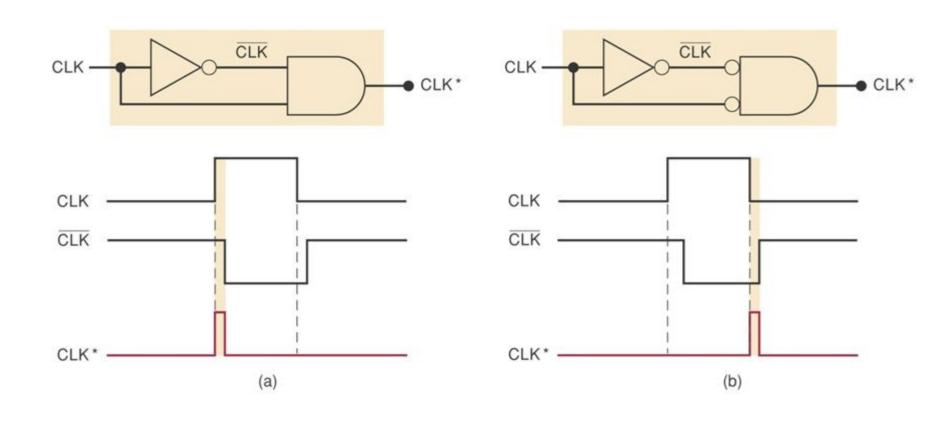

# Detector de bordas

"Positive edge-detection circuit"

### Detectores de Bordas

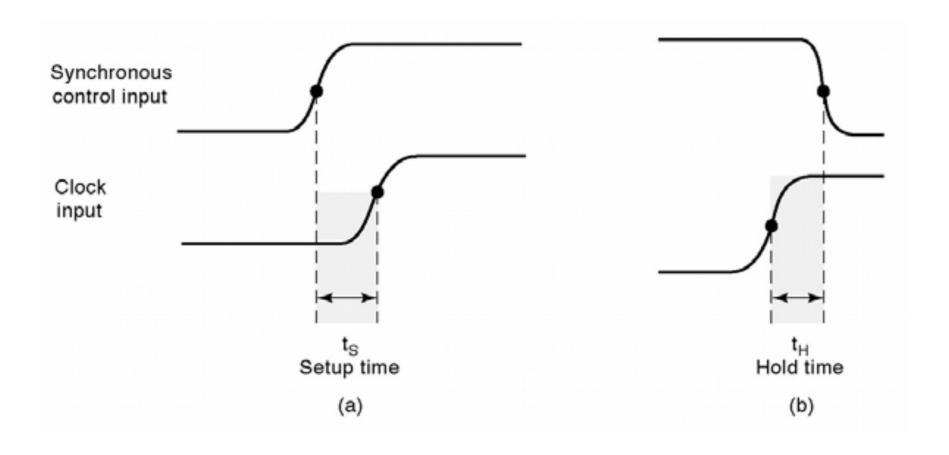

## Parâmetros no tempo:

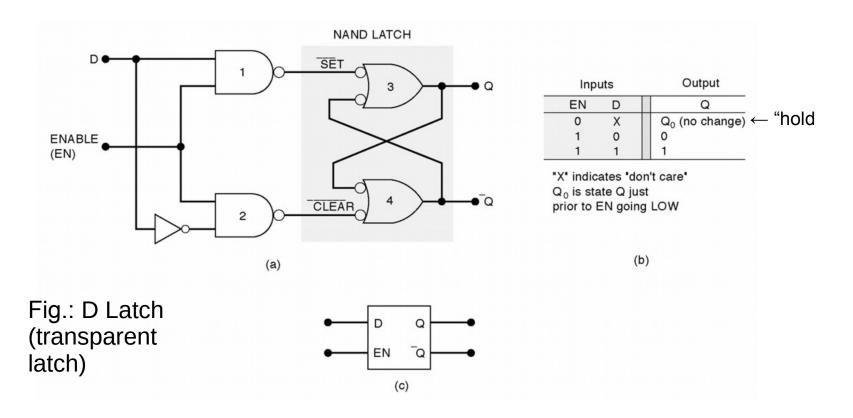

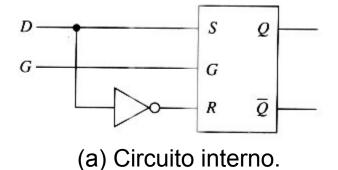

### Latch Tipo D:

Tabela verdade do RS:

Set Reset Q(t+1) Obs:

0 0 Q(t) Mantêm estado.

1 0 1 Set

0 1 0 Reset

1 1 1 Condição inválida

b) Tabela verdade do Latch D:

| G | D | Q(t+1) | Obs:           |

|---|---|--------|----------------|

| 0 | X | Q(t)   | Mantêm estado. |

| 1 | 0 | 1      | Reset          |

| 1 | 1 | 1      | Set            |

c) Diagrama de estados.

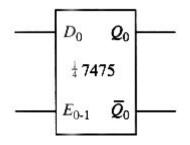

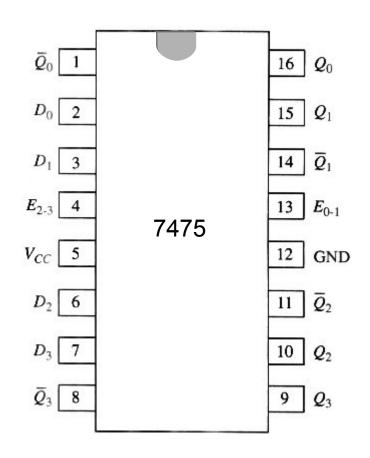

#### CI comercial:

#### Completar:

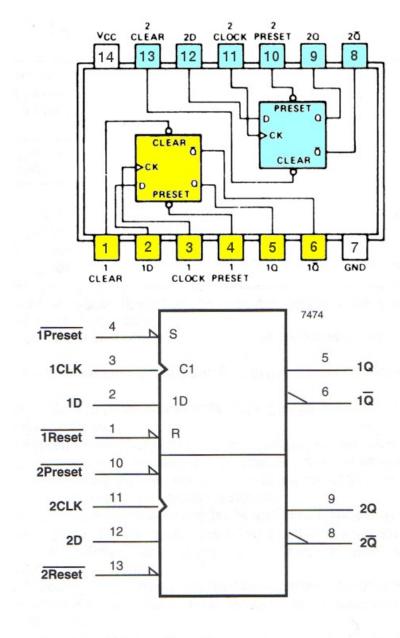

### Biestáveis D comerciais

• 7474: Flip-Flop D,

• 7475: Latch D,

## 74LS74 Flip-Flop

Biestáveis 11/03/19 <a>⊅ pág 36</a>

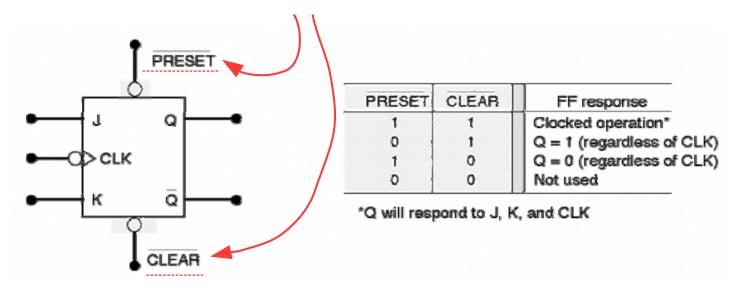

### Entradas assíncronas...

- Num FF-D ou FF-JK, as entradas D, J ou K são ditas "síncronas" porque seu efeito na saída do FF depende da sincronização com o sinal de "clock".

- Entradas assíncronas ( PRESET, CLEAR ): sobre-escrevem as entradas síncronas; operam de forma independente das entradas síncronas e do sinal de clock e são usadas para ajustar ("forçar") um FF para o estado 0 ou 1 em qualquer instante de tempo (principalmente quando recém se alimenta um circuito, para garantir sua condição inicial).

## 74LS74 Flip-Flop

#### AC CHARACTERISTICS (T<sub>A</sub> = 25°C, V<sub>CC</sub> = 5.0 V)

|                  |                             |     | Limits |     |      |                 |                                                     |

|------------------|-----------------------------|-----|--------|-----|------|-----------------|-----------------------------------------------------|

| Symbol           | Parameter                   | Min | Тур    | Max | Unit | Test Conditions |                                                     |

| fMAX             | Maximum Clock Frequency     | 25  | 33     |     | MHz  | Figure 1        | .,,                                                 |

| <sup>t</sup> PLH | Clock, Clear, Set to Output |     | 13     | 25  | ns   | Figure 1        | $V_{CC} = 5.0 \text{ V}$<br>$C_{L} = 15 \text{ pF}$ |

| <sup>t</sup> PHL | Clock, Clear, Set to Output |     | 25     | 40  | ns   | Figure          |                                                     |

#### AC SETUP REQUIREMENTS $(T_A = 25^{\circ}C)$

|                    |                        | Limits |     |     |      |                        |                         |

|--------------------|------------------------|--------|-----|-----|------|------------------------|-------------------------|

| Symbol             | Parameter              | Min    | Тур | Max | Unit | <b>Test Conditions</b> |                         |

| <sup>t</sup> W (H) | Clock                  | 25     |     |     | ns   | Figure 1               |                         |

| tW(L)              | Clear, Set             | 25     |     |     | ns   | Figure 2               |                         |

|                    | Data Setup Time — HIGH | 20     |     |     | ns   | Eiguro 1               | V <sub>CC</sub> = 5.0 V |

| t <sub>S</sub>     | LOW                    | 20     |     |     | ns   | Figure 1               |                         |

| <sup>t</sup> h     | Hold Time              | 5.0    |     |     | ns   | Figure 1               |                         |

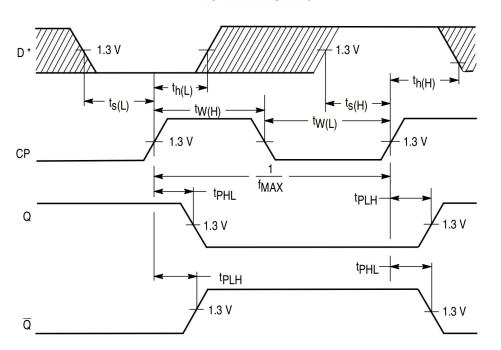

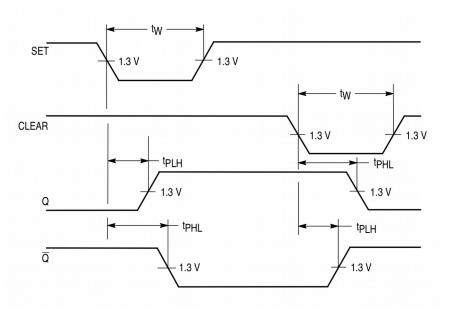

### Parâmetros AC

#### **AC WAVEFORMS**

\*The shaded areas indicate when the input is permitted to change for predictable output performance.

$t_p$  = propagation delay;

$t_s$  = setup time;

$t_h$  = hold time;

$t_{w}$  = assyncronous times.

| IVICAC           |                             |    |    |    | ,        |                                                     |

|------------------|-----------------------------|----|----|----|----------|-----------------------------------------------------|

| <sup>t</sup> PLH | Olaski, Olaski, Ostanit     | 13 | 25 | ns | Figure 1 | $V_{CC} = 5.0 \text{ V}$<br>$C_{I} = 15 \text{ pF}$ |

| <sup>t</sup> PHL | Clock, Clear, Set to Output | 25 | 40 | ns | Figure 1 | - L                                                 |

#### AC SETUP REQUIREMENTS (T<sub>A</sub> = 25°C)

|                |                        |     | Limits |     |      |                        |                         |

|----------------|------------------------|-----|--------|-----|------|------------------------|-------------------------|

| Symbol         | Parameter              | Min | Тур    | Max | Unit | <b>Test Conditions</b> |                         |

| tW(H)          | Clock                  | 25  |        |     | ns   | Figure 1               |                         |

| tW(L)          | Clear, Set             | 25  |        |     | ns   | Figure 2               |                         |

|                | Data Setup Time — HIGH | 20  |        |     | ns   | Figure 1               | V <sub>CC</sub> = 5.0 V |

| t <sub>S</sub> | LOW                    | 20  |        |     | ns   | Figure 1               |                         |

| th             | Hold Time              | 5.0 |        |     | ns   | Figure 1               |                         |

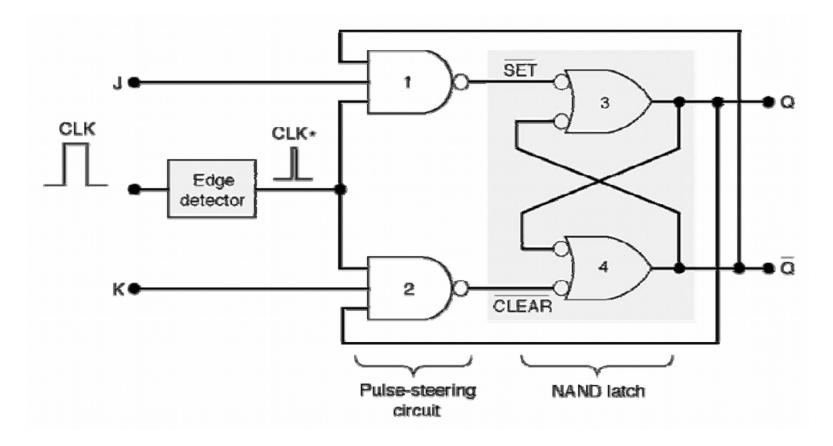

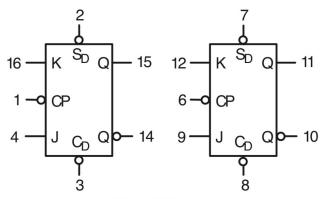

## Flip-Flop JK:

Circuito interno

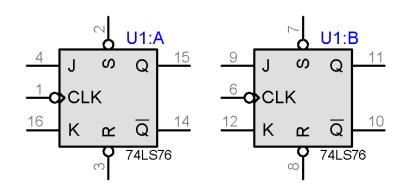

## Flip-Flop JK:

Ex.: 74LS76:

LOGIC SYMBOL

$V_{CC} = PIN 5$ GND = PIN 13

#### **MODE SELECT – TRUTH TABLE**

| OPERATING        |                  | INP              | OUTPUTS |   |                |   |

|------------------|------------------|------------------|---------|---|----------------|---|

| MODE             | $\overline{S}_D$ | $\overline{C}_D$ | J       | K | Q              | Q |

| Set              | L                | Н                | Х       | Х | Н              | L |

| Reset (Clear)    | Н                | L                | Х       | Х | L              | Н |

| *Undetermined    | L                | L                | Х       | Х | Н              | Н |

| Toggle           | Н                | Н                | h       | h | $\overline{q}$ | q |

| Load "0" (Reset) | Н                | Н                | I       | h | L              | Н |

| Load "1" (Set)   | Н                | Н                | h       | I | Н              | L |

| Hold             | Н                | Н                | I       | ĺ | q              | q |

\* Both outputs will be HIGH while both  $\overline{S}_D$  and  $\overline{C}_D$  are LOW, but the output states are unpredictable if  $\overline{S}_D$  and  $\overline{C}_D$  go HIGH simultaneously.

H, h = HIGH Voltage Level

L, I = LOW Voltage Level

X = Immaterial

I, h (q) = Lower case letters indicate the state of the referenced input (or output) one setup time prior to the HIGH-to-LOW clock transition

Dados: On Semiconductor (Division of Motorola; http://onsemi.com)

### FF-JK: 74LS76

#### AC CHARACTERISTICS (TA = 25°C, VCC = 5.0 V)

|                  |                             | Limits |     | Limits |      |                                                |  |

|------------------|-----------------------------|--------|-----|--------|------|------------------------------------------------|--|

| Symbol           | Parameter                   | Min    | Тур | Max    | Unit | Test Conditions                                |  |

| f <sub>MAX</sub> | Maximum Clock Frequency     | 30     | 45  |        | MHz  | 1200 - 7 - 2 - 2                               |  |

| t <sub>PLH</sub> | Clock Cloor Set to Output   |        | 15  | 20     | ns   | $V_{CC} = 5.0 \text{ V}$ $C_L = 15 \text{ pF}$ |  |

| t <sub>PHL</sub> | Clock, Clear, Set to Output |        | 15  | 20     | ns   |                                                |  |

#### AC SETUP REQUIREMENTS (TA = 25°C)

|                |                        |     | Limits |     | Limits |                         |  |  |

|----------------|------------------------|-----|--------|-----|--------|-------------------------|--|--|

| Symbol         | Parameter              | Min | Тур    | Max | Unit   | Test Conditions         |  |  |

| t <sub>W</sub> | Clock Pulse Width High | 20  |        |     | ns     |                         |  |  |

| t <sub>W</sub> | Clear Set Pulse Width  | 25  |        |     | ns     | V F O V                 |  |  |

| ts             | Setup Time             | 20  |        |     | ns     | V <sub>CC</sub> = 5.0 V |  |  |

| th             | Hold Time              | 0   |        |     | ns     |                         |  |  |

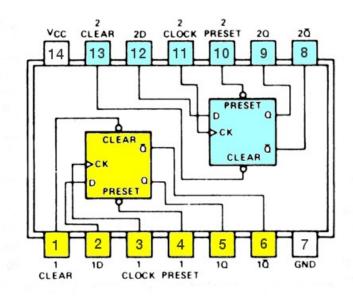

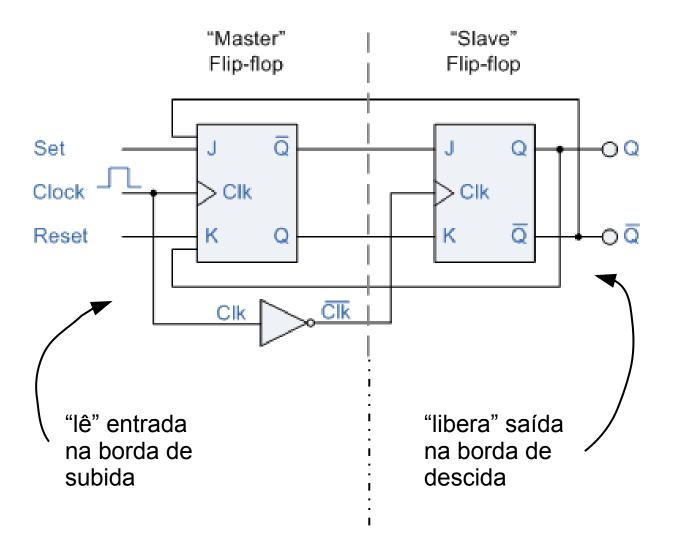

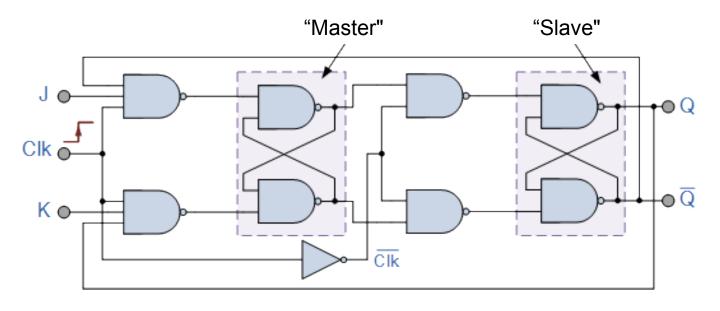

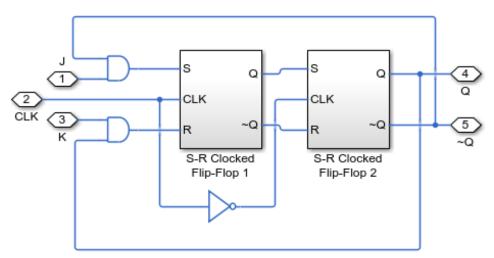

## FF RS MS (Master-Slave)

## FF JK MS (Master Slave)

## Atenção: 74LS76 ≠ 7476!

#### SN74LS76A

### **Dual JK Flip-Flop**with Set and Clear

The SN74LS76A offers individual J, K, Clock Pulse, Direct Set and Direct Clear inputs. These dual flip-flops are designed so that when the clock goes HIGH, the inputs are enabled and data will be accepted. The Logic Level of the J and K inputs will perform according to the Truth Table as long as minimum set-up times are observed. Input data is transferred to the outputs on the HIGH-to-LOW clock transitions.

#### 'LS76A FUNCTION TABLE

|     | IN  | OUT | PUTS |   |                |                       |

|-----|-----|-----|------|---|----------------|-----------------------|

| PRE | CLR | CLK | J    | K | a              | ā                     |

| L   | Н   | ×   | X    | Х | Н              | L                     |

| н   | L   | ×   | X    | X | L              | Н                     |

| L   | L   | ×   | X    | X | H <sup>†</sup> | нţ                    |

| н   | н   | 1   | L    | L | $a_0$          | $\overline{\alpha}_0$ |

| н   | Н   | 1   | Н    | L | н              | L                     |

| н   | Н   | 1   | L    | Н | L              | н                     |

| н   | Н   | 1   | Н    | Н | TOG            | GLE                   |

| н   | Н   | Н   | X    | X | $\alpha_0$     | $\overline{\alpha}_0$ |

Revised July 2001

September 1986

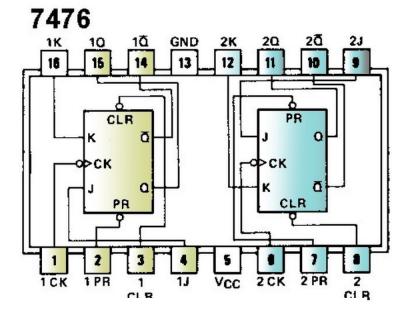

#### **DM7476**

**Dual Master-Slave J-K Flip-Flops with Clear, Preset, and Complementary Outputs**

'76

FUNCTION TABLE

|     | IN  | OUT | PUTS |   |                |                       |

|-----|-----|-----|------|---|----------------|-----------------------|

| PRE | CLR | CLK | J    | K | Q              | ā                     |

| L   | Н   | X   | X    | X | Н              | L                     |

| н   | L   | ×   | X    | × | L L            | н                     |

| L   | L   | X   | X    | X | Нţ             | нt                    |

| н   | Н   | л.  | L    | L | α <sub>0</sub> | $\overline{\alpha}_0$ |

| н   | Н   | 1   | H    | L | н              | L                     |

| н   | Н   | л.  | L    | Н | L              | н                     |

| н   | Н   | 工   | Н    | н | TOGGLE         |                       |

<sup>†</sup> This configuration is nonstable; that is, it will not persist when either preset or clear returns to its inactive (high) level.

FAIRCHILD SEMICONDUCTORIM