Exemplos Projetos Contadores Assíncronos:

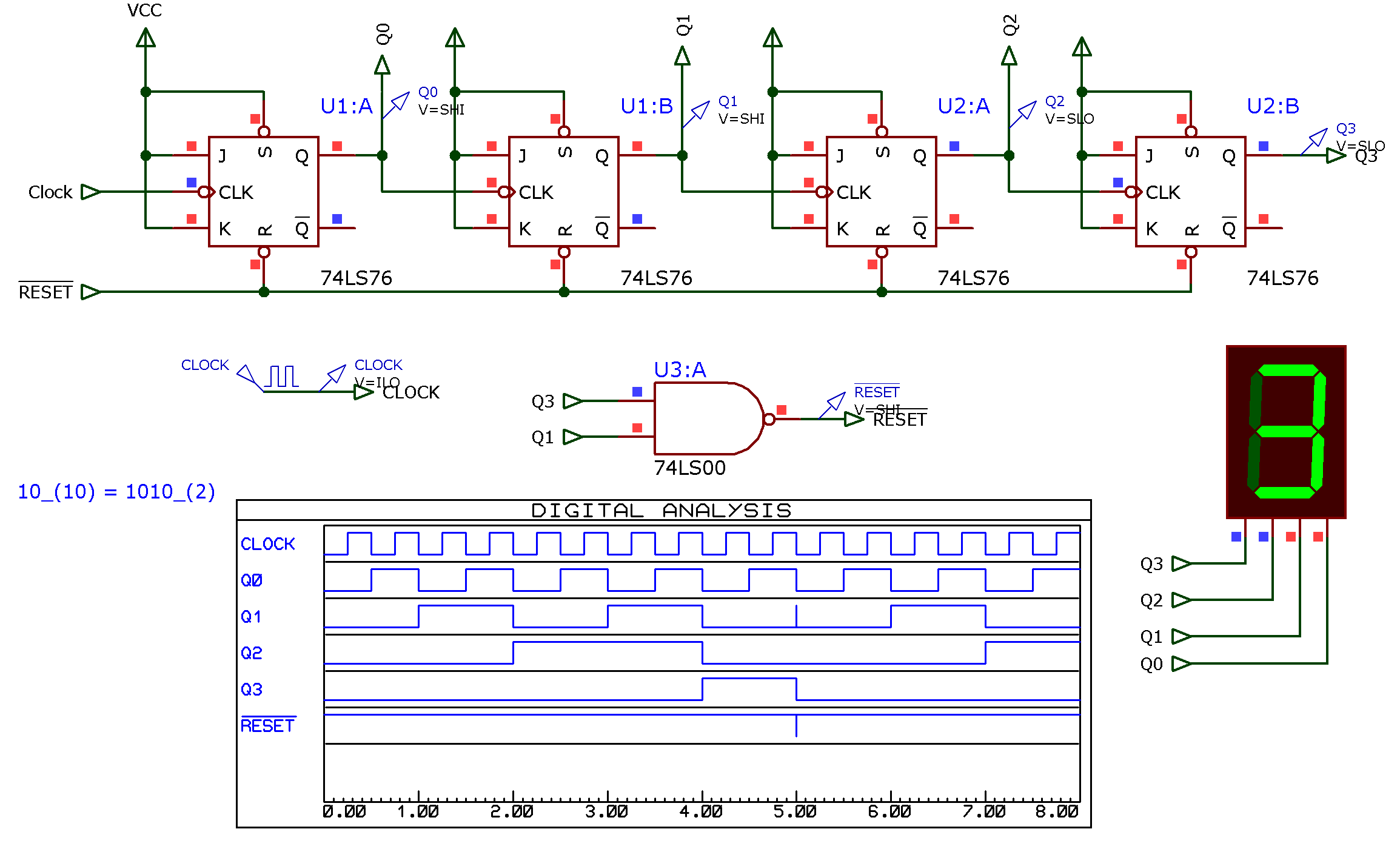

Exemplo_1: Contador assíncrono cresente de 0 à 9:

Solução:

- O maior valor atingido na contagem é

- Montar um circuito assíncrono crescente com 4 FF's. Inicialmente ele contaria de 0 até 15.

- Modificar o circuito para um sinal de

Circuito final:

contador_assync_mod10_crescente.DSN (arquivo criado originalmente no Proteux 7.8 SP2).

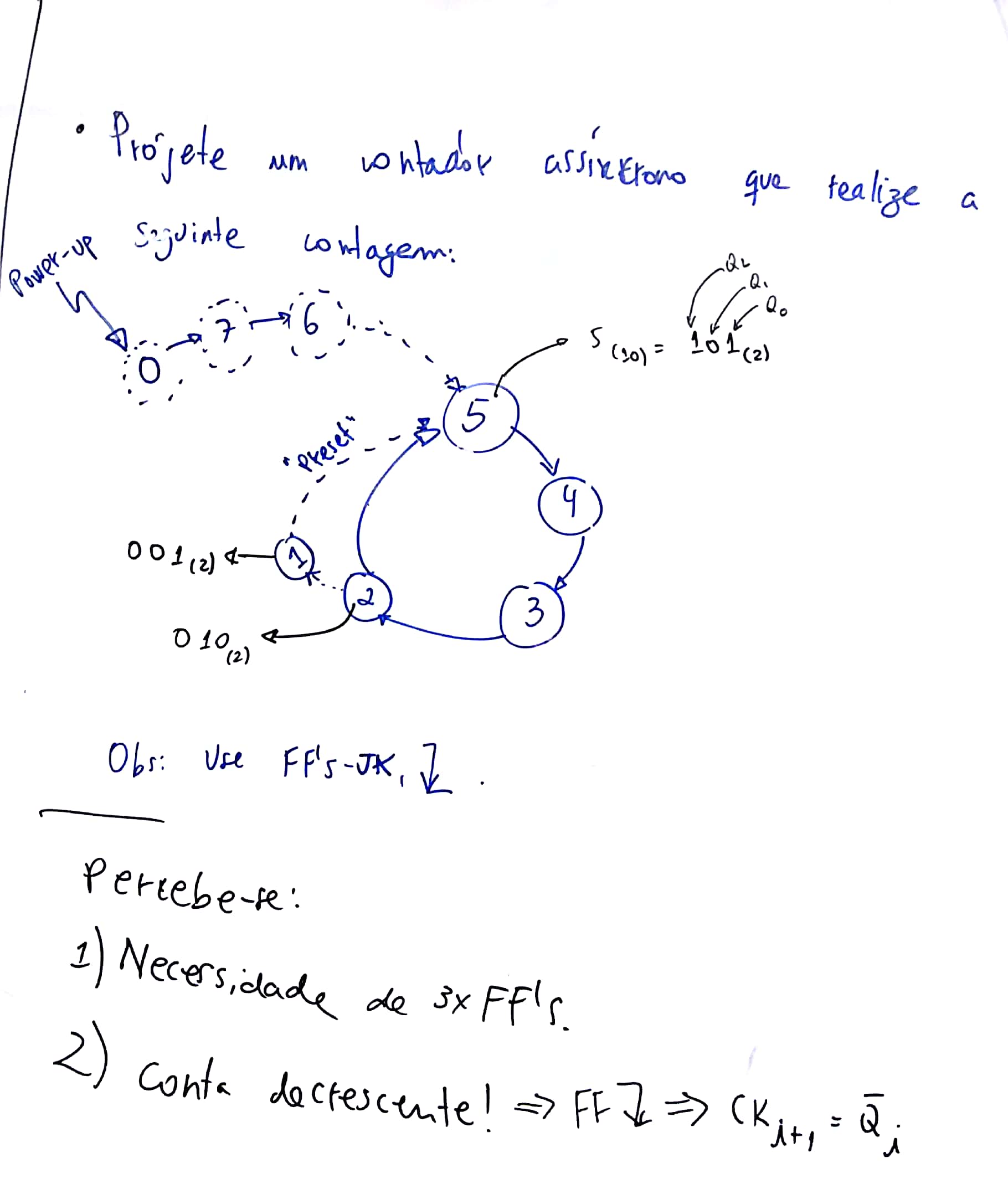

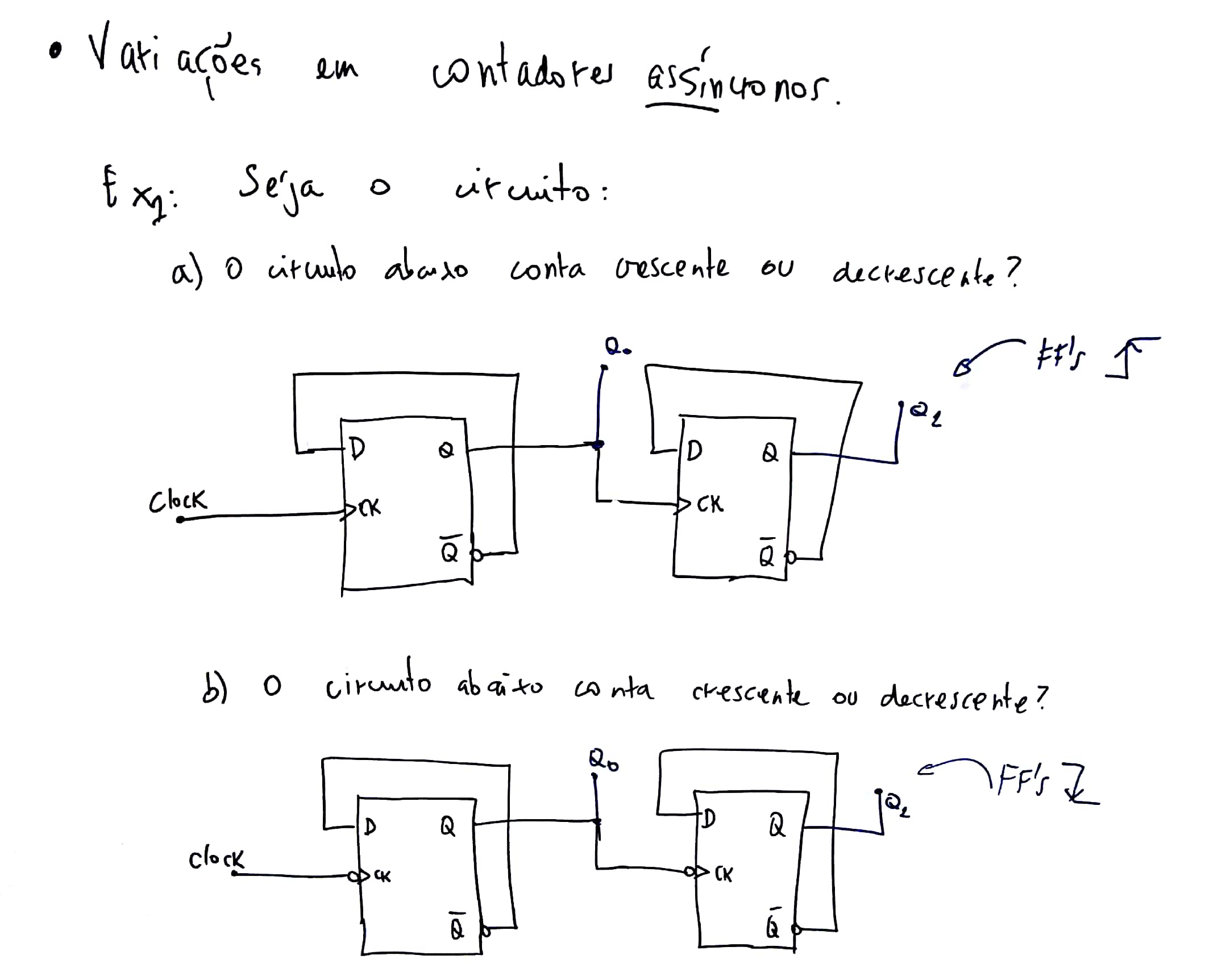

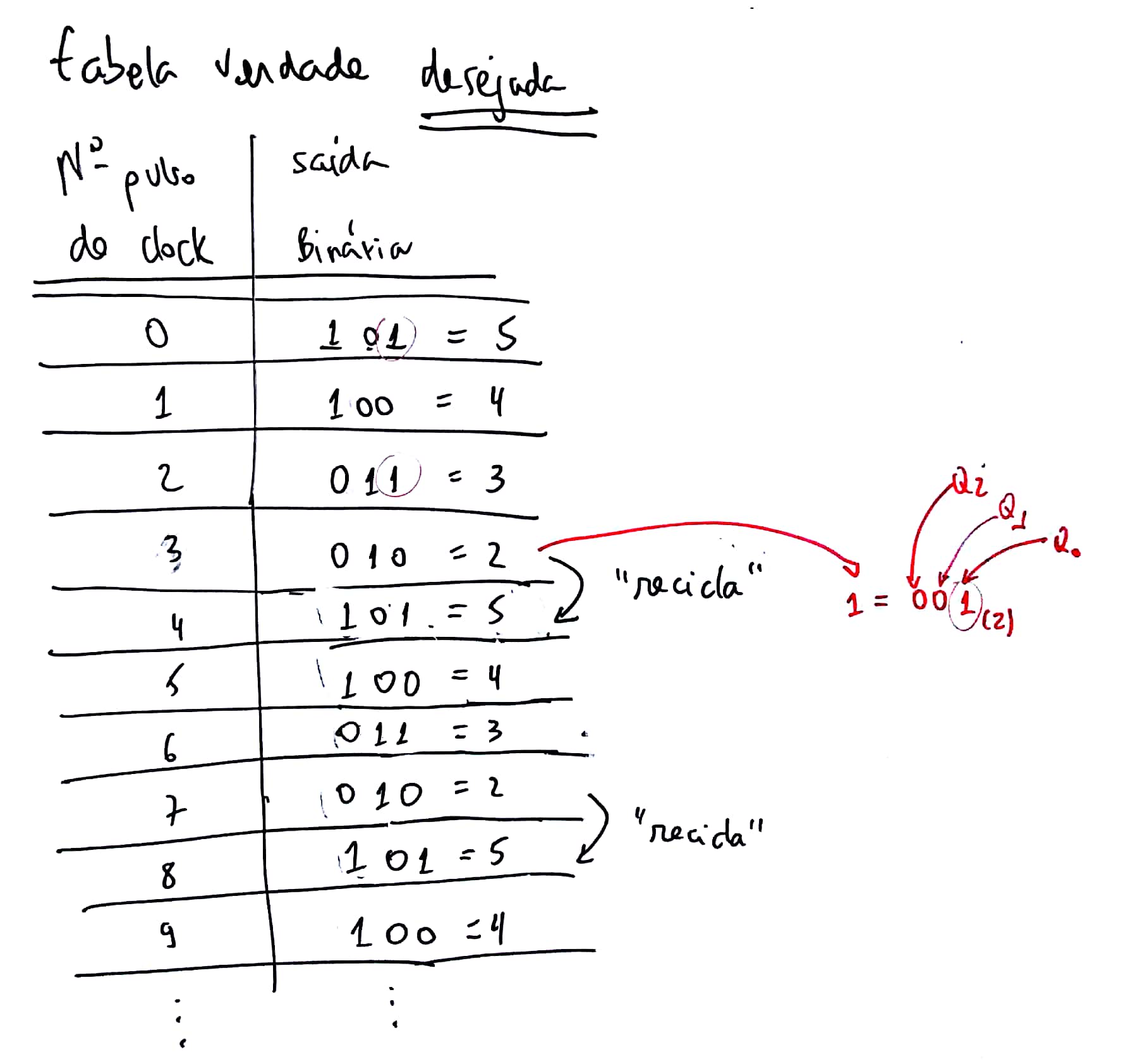

Exemplo_2: projetar contador assícrono (usando FF's JK borda de descida) capaz de realizar a sequencia de contagem abaixo: (Aula de 14/04/2028)

Note: é um contador decrescente!

Cuidado com soluções "decoradas":

Solução simples:

Estrutura de contador assíncrono descrescente

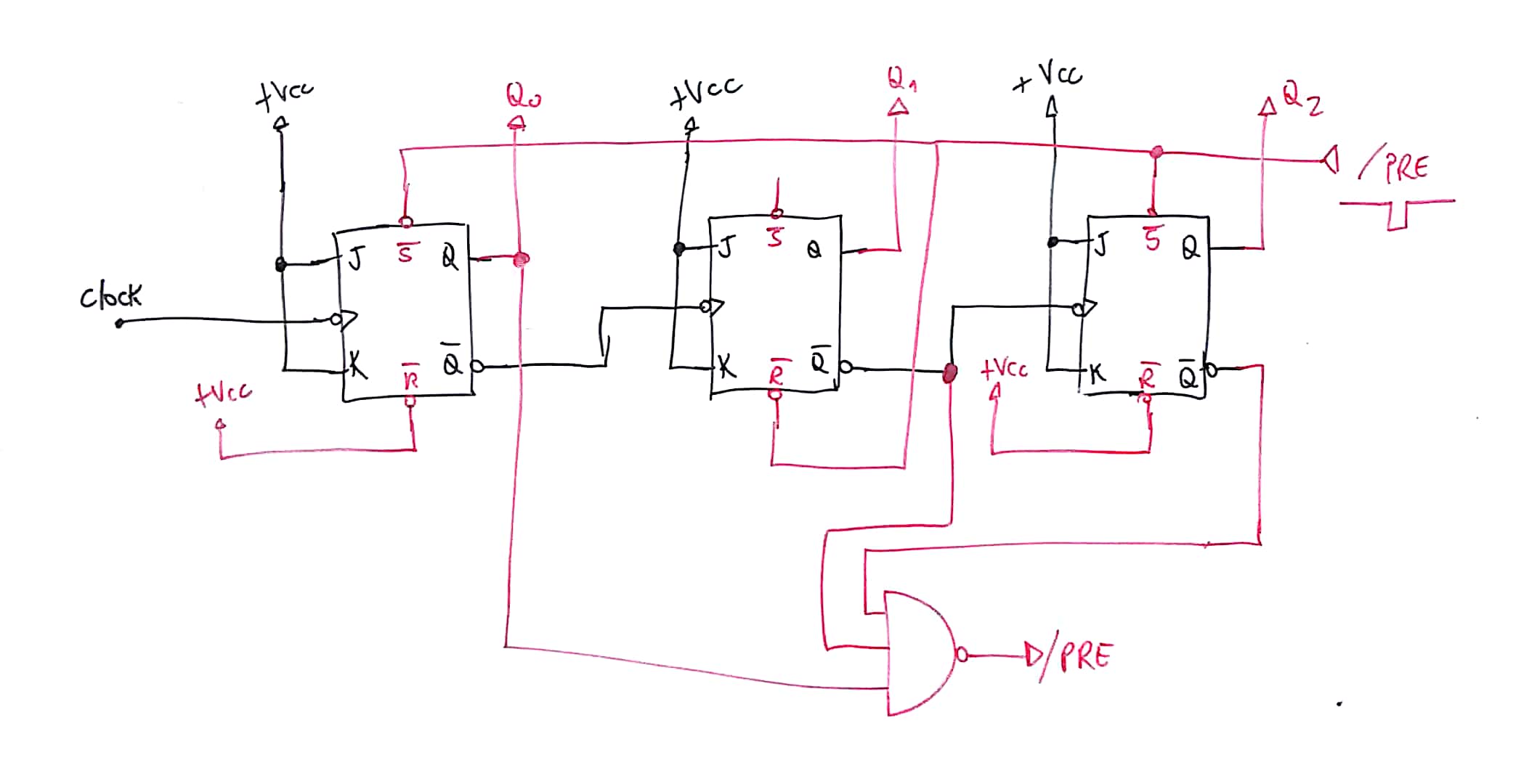

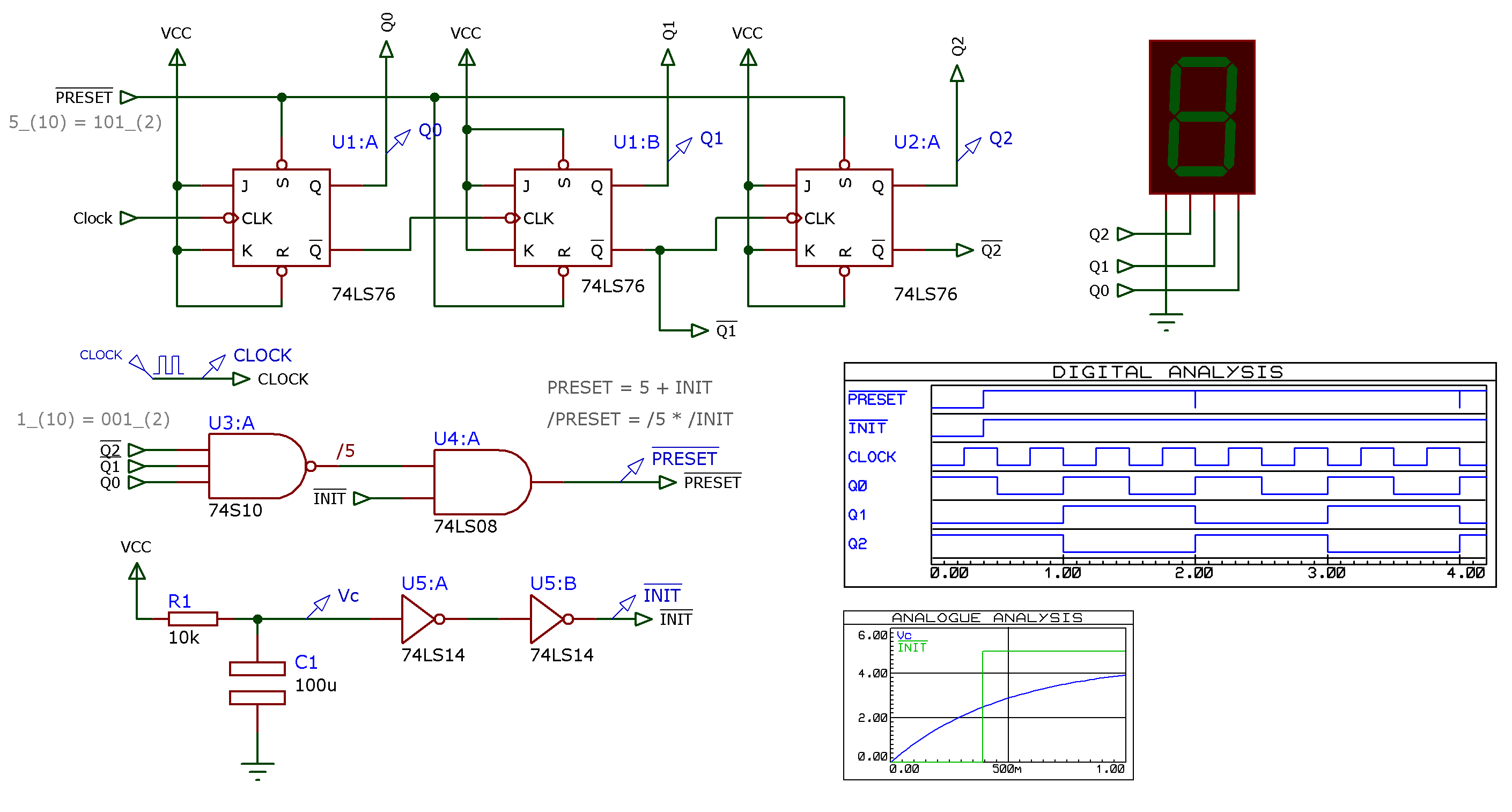

Solução: contador decrescente de 5 até 2:

Repare como deve ser detectado o ponto de reciclagem (e notar que este circuito gera sequencia decescente de contagem: ficar atento a sequencia binária assumida!)

Note a sequencia de contagem:

Circuito simulado no Proteus:

contador_assync_decrescente_5_to_2.DSN

Observações:

À primeira solução foi acrescentado um circuito de "Power-up" formado pelo resistor e capacitor, de forma que quando a alimentação fosse fornecida ao circuito, o mesmo iniciasse no número 5 e não outro ponto qualquer da contagem.

Note que enquanto o capacitor demora para carregar, é gerado um nível lógico baixo na saída

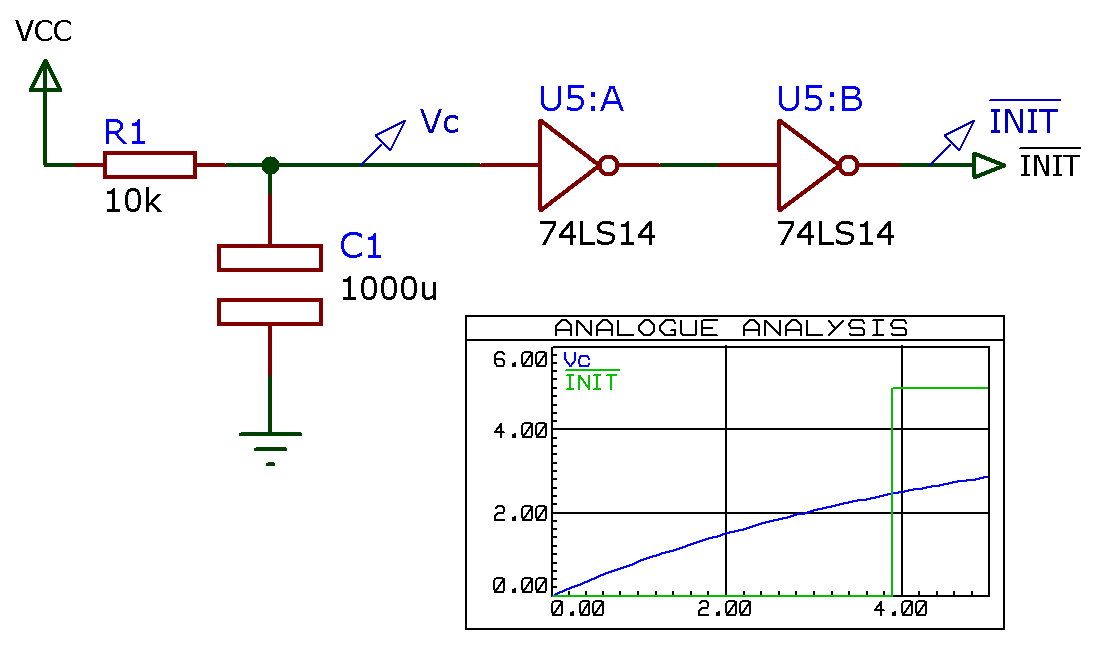

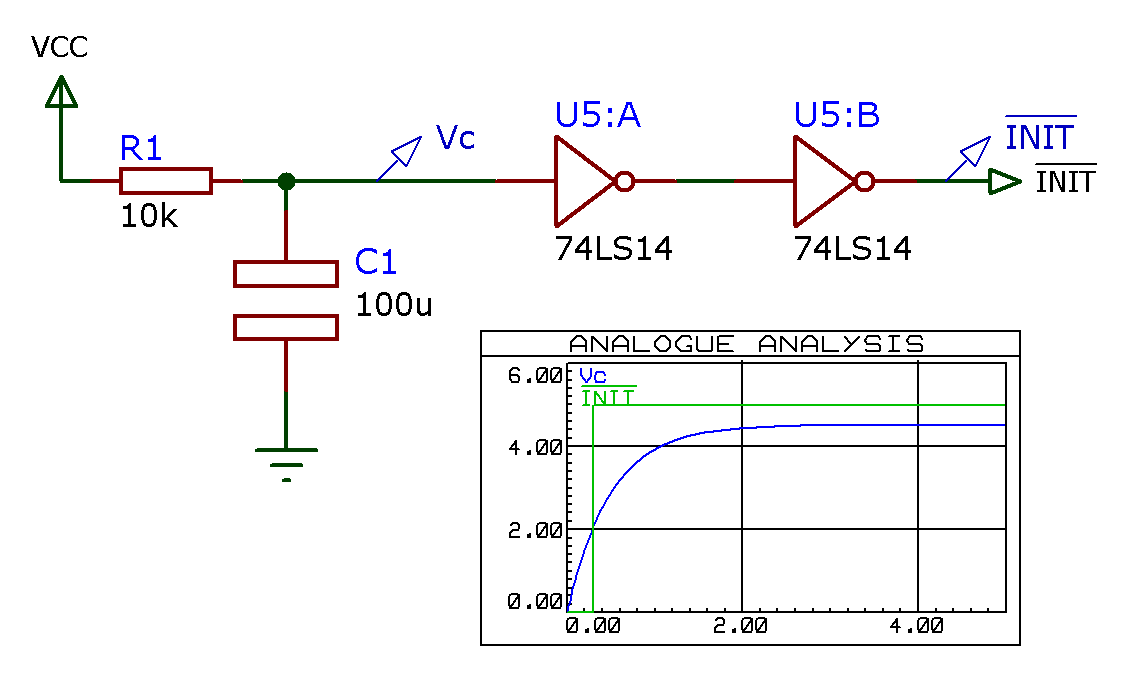

Circuito com C=1000 uF Circuito com C=100 uF

Note que foi acrescentada uma porta Schmidtt-triger na saída do circuito RC para "transformar" o sinal analógico de tensão de carregamento do capacitor num sinal compatível com níveis TTL (notar o

Note ainda que como queríamos que circuito iniciasse no número 5 e que toda vez que atingisse o final de contagem fosse "reprogramado" no número 5, o sinal de

Usando pastilhas de CIs contadores Assíncronos

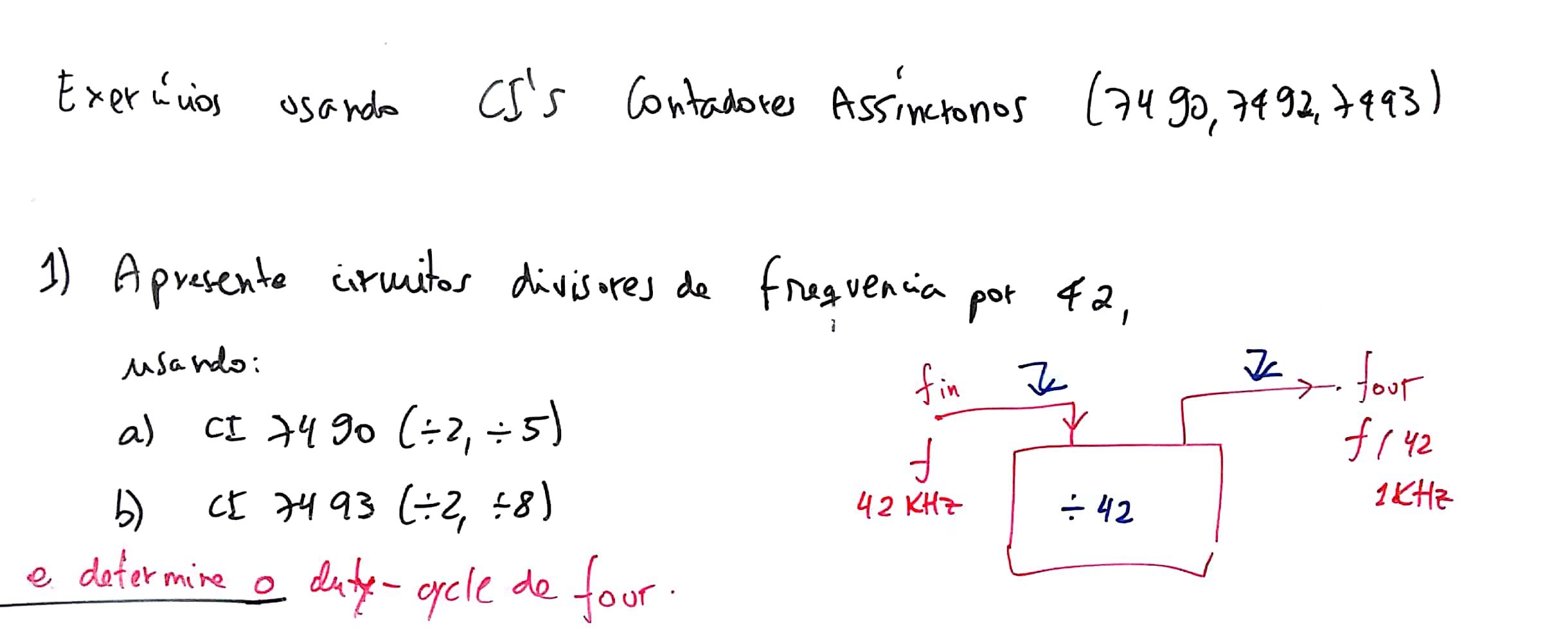

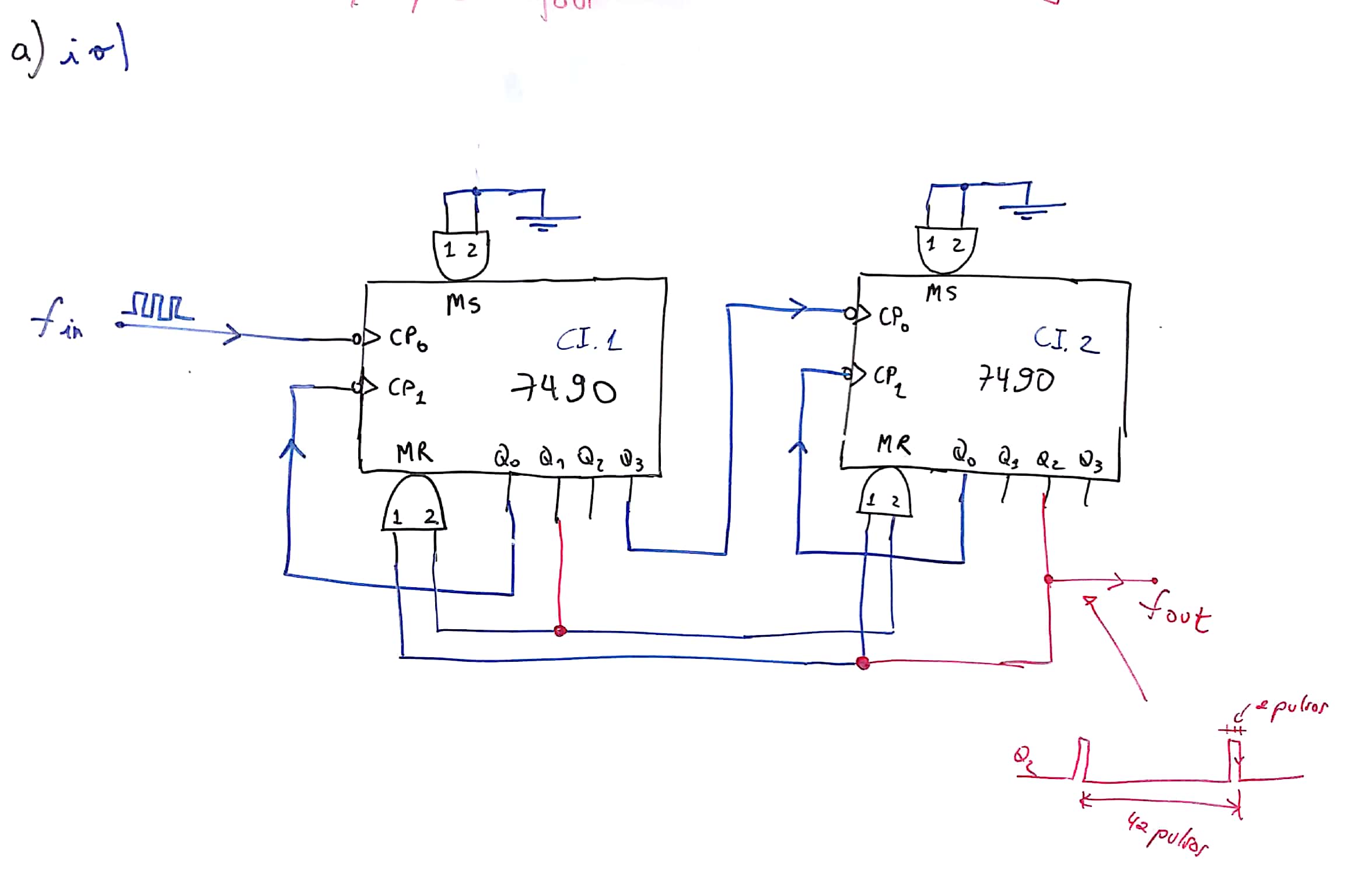

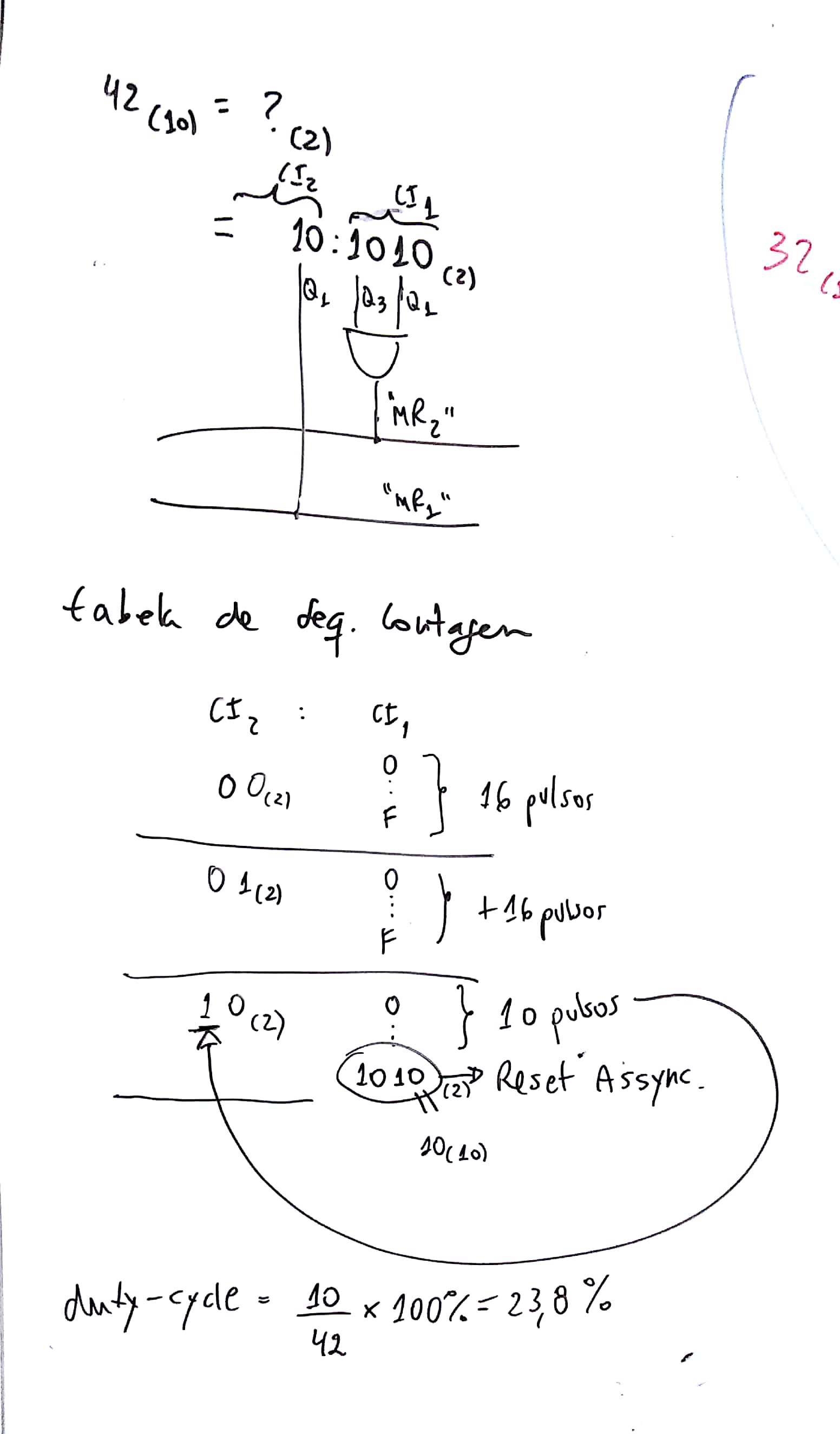

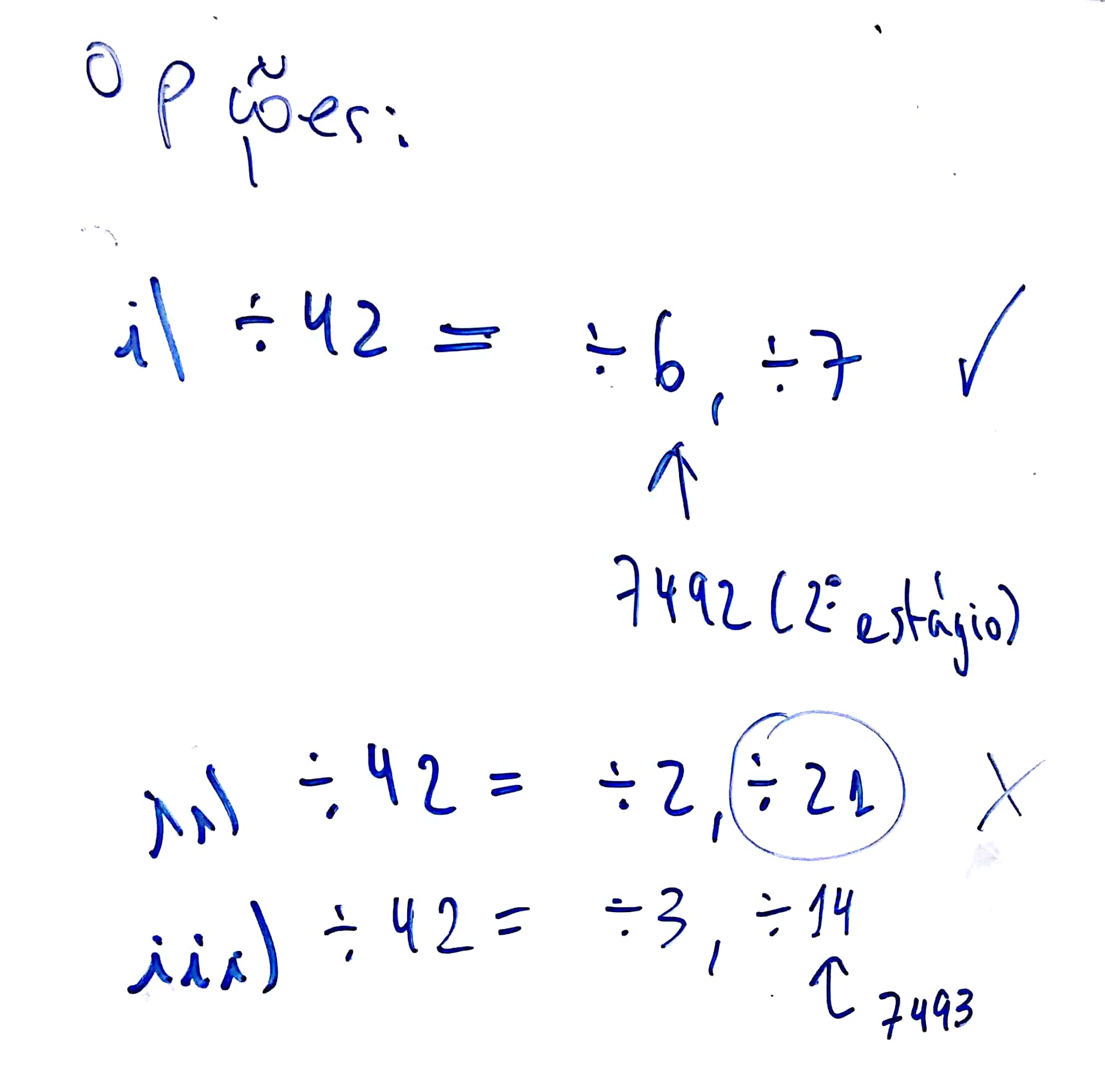

Exemplo_3: Use pastilhas 74LS90 e/ou 74LS93 para criar um divisor de frequencia por 42:

Note a diferença na contagem realizada entre a pastilha 7490 x 7493:

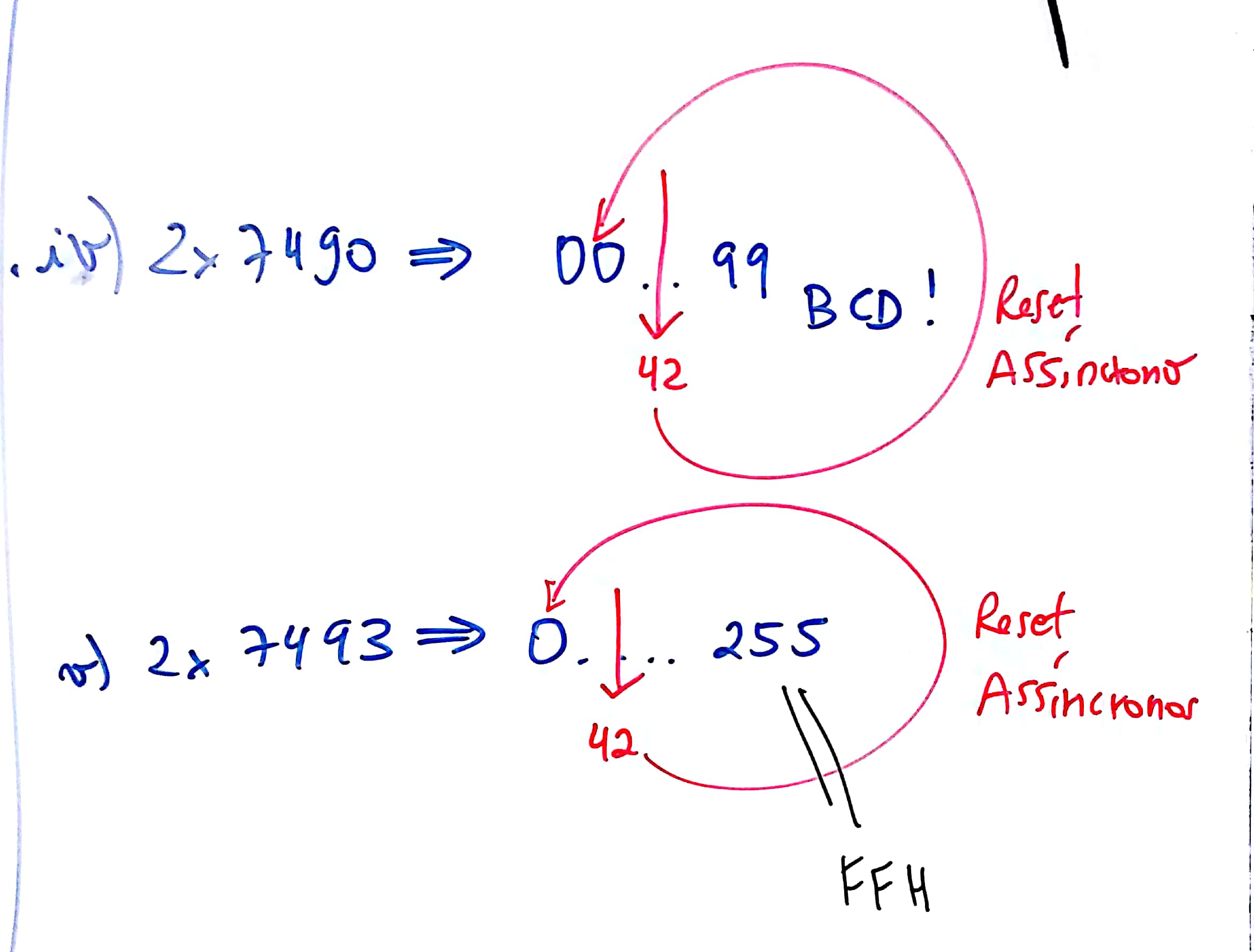

Soluções possíveis:

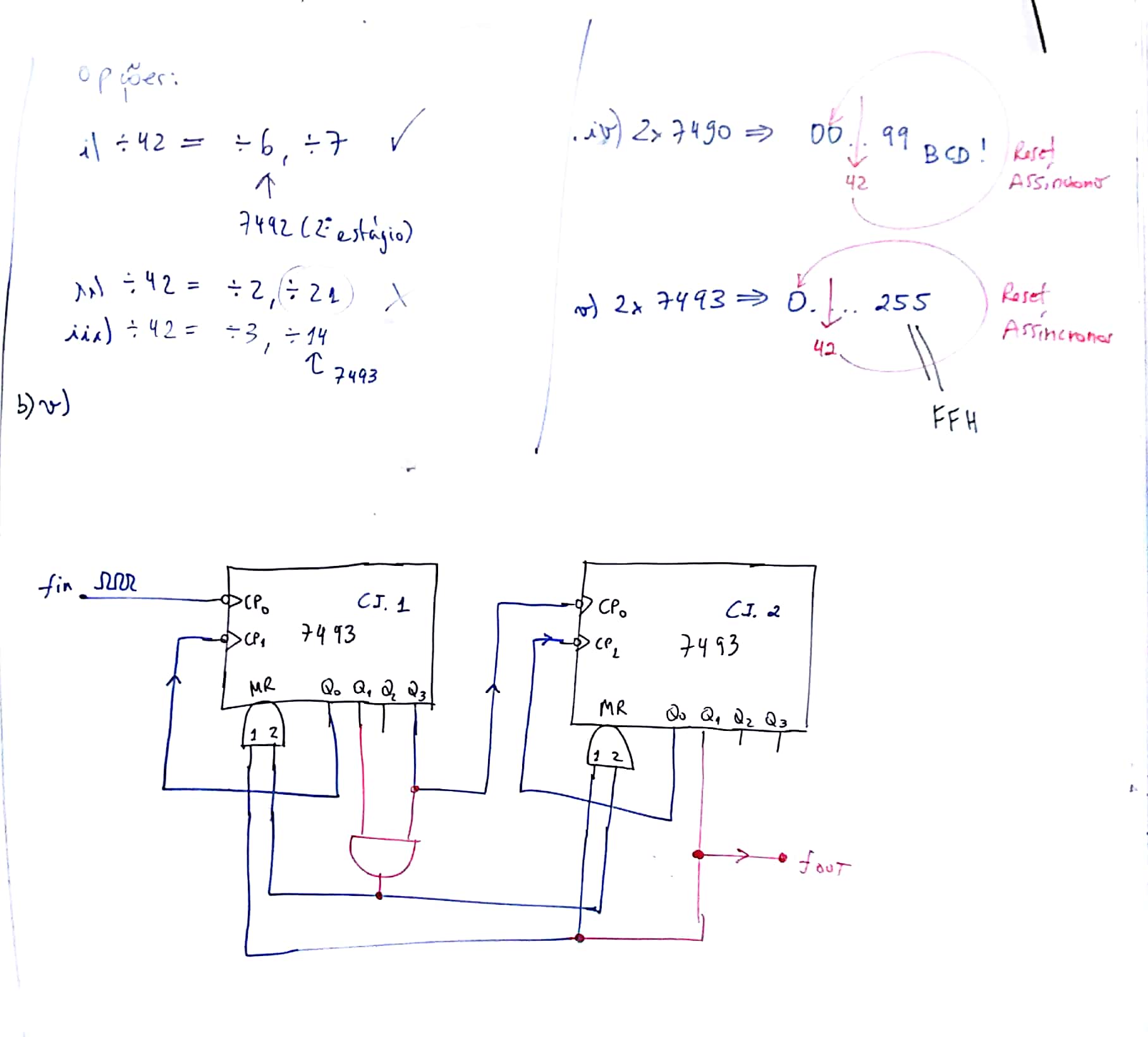

Note: contador 74LS93 forma contagem binária na sua saída (não decimal!):

xxxxxxxxxx42 | 16-----------32 2---10

Por isto que devemos detectar: Q1=1 e Q3=1 no estágio "LSB" e Q1=1 no estágio "MSB" do ciruito contador.

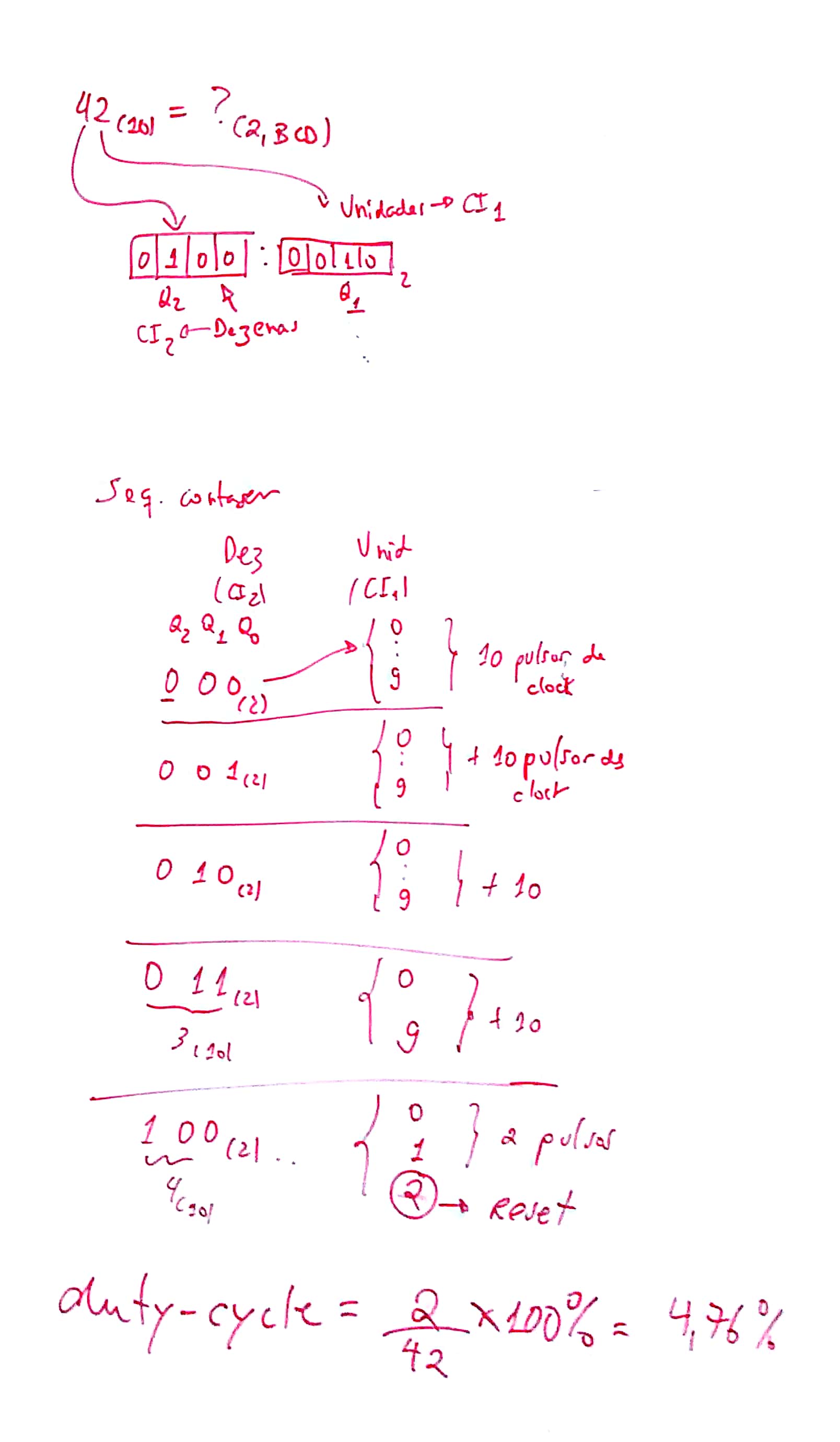

- E como seria a solução usando 74LS90 (Contador Decimal)?

E preocupação extra: como fica o "duty-cycle"?

Note um detalhe "preocupante" nesta solução:

Em comparação, o duty-cycle usando o 74LS93 fica:

Outras soluções:

Fernando Passold, em 12/04/2020; 27/08/2021.