Projeto Contador Síncrono 2024/1

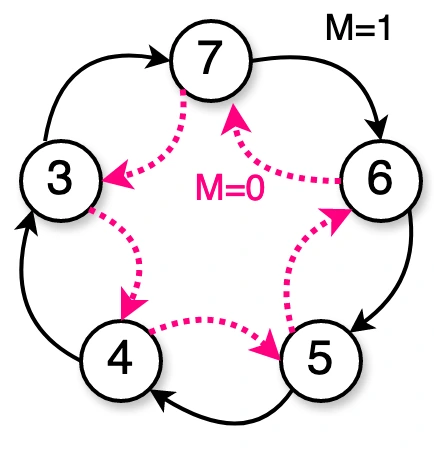

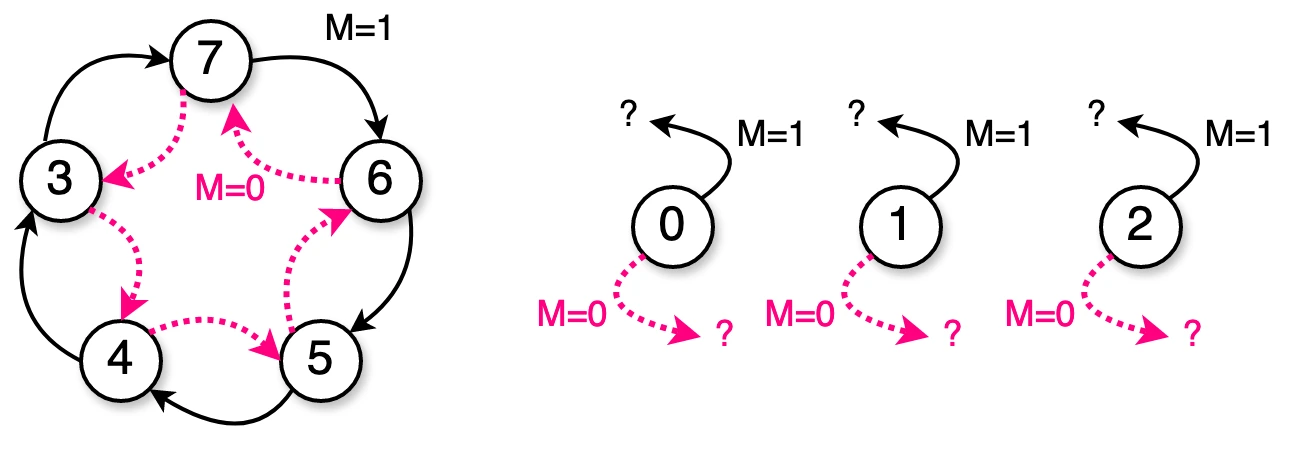

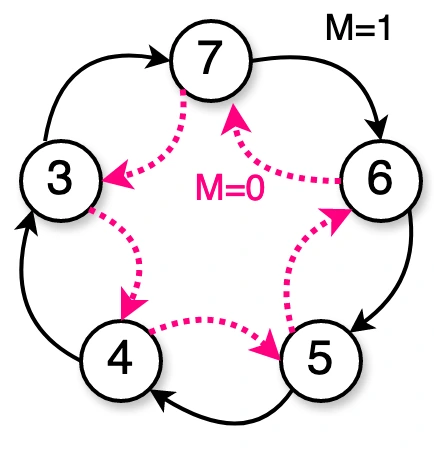

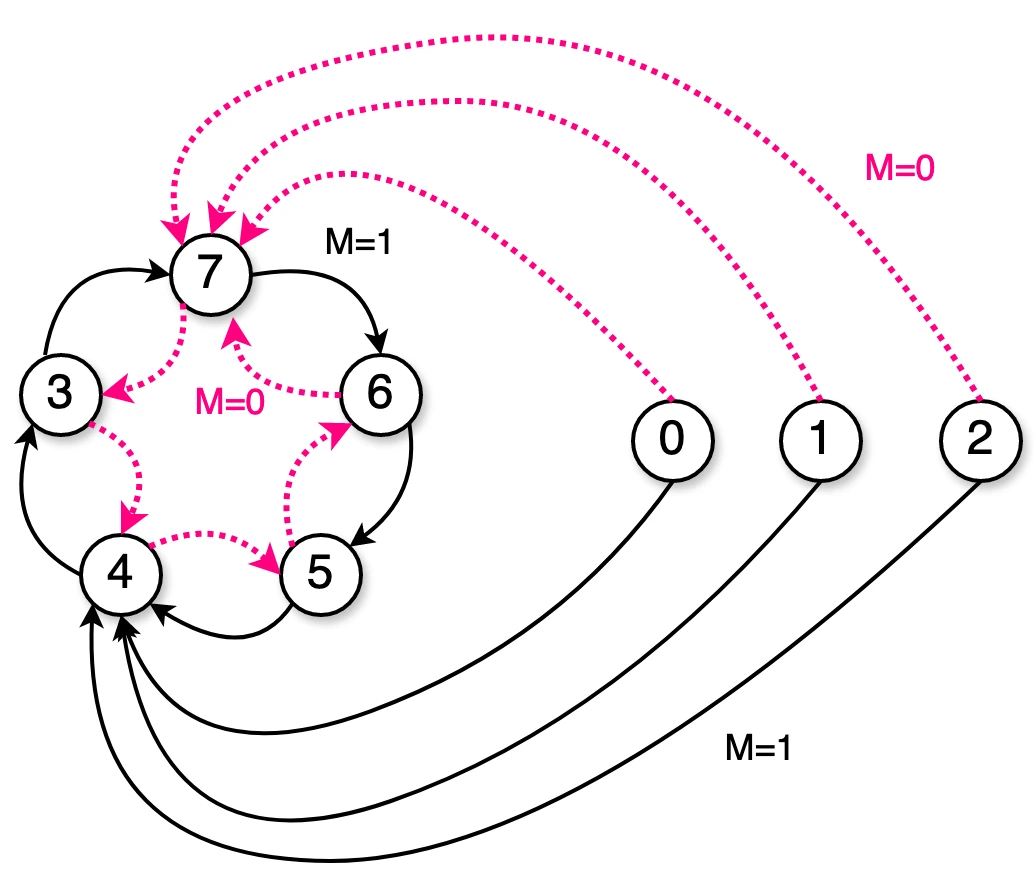

Suponha que queiramos construir um contador síncrono capaz de executar a seguinte sequência de contagem:

Obs.: A variável serve para ajustar o sentido da contagem. Funcionaria como a entrada de um CI 74LS190.

Projeto ?

Notamos que o maior valor assumido nesta contagem é e o menor valor é , o que significa que FF's bastam para resolver este circuito. Resta escolher que tipo de FF adotar. Se usarmos FF´s-JK será necessário deduzir equações (circuitos). Se optarmos por FF´s-D, teremos que deduzir apenas 1 circuito (equação) por FF.

Seque tabela de sequência de contagem deste contador:

xxxxxxxxxxRef | m q2 q1 q0 | Q2 Q1 Q0 | d2 d1 d0 | Obs: q(t) --> Q(t+1)----+------------+----------+----------+---------------------0 | 0 0 0 0 | X X X | X X X | 0 --> X1 | 0 0 0 1 | X X X | X X X | 1 --> X2 | 0 0 1 0 | X X X | X X X | 2 --> X----+------------+----------+----------+---------------------3 | 0 0 1 1 | 1 0 0 | 1 0 0 | 3 --> 44 | 0 1 0 0 | 1 0 1 | 1 0 1 | 4 --> 55 | 0 1 0 1 | 1 1 0 | 1 1 0 | 5 --> 66 | 0 1 1 0 | 1 1 1 | 1 1 1 | 6 --> 77 | 0 1 1 1 | 0 1 1 | 0 1 1 | 7 --> 3----+------------+----------+----------+---------------------8 | 1 0 0 0 | X X X | X X X | 0 --> X9 | 1 0 0 1 | X X X | X X X | 1 --> X10 | 1 0 1 0 | X X X | X X X | 2 --> X----+------------+----------+----------+---------------------11 | 1 0 1 1 | 1 1 1 | 1 1 1 | 3 --> 712 | 1 1 0 0 | 0 1 1 | 0 1 1 | 4 --> 313 | 1 1 0 1 | 1 0 0 | 1 0 0 | 5 --> 414 | 1 1 1 0 | 1 0 1 | 1 0 1 | 6 --> 515 | 1 1 1 1 | 1 1 0 | 1 1 0 | 7 --> 6

Lembrando que a tabela de transição do FF-D é:

xxxxxxxxxxq(t) --> Q(t+1) | D----------------+---0 ---> 0 | 00 ---> 1 | 11 ---> 0 | 01 ---> 1 | 1

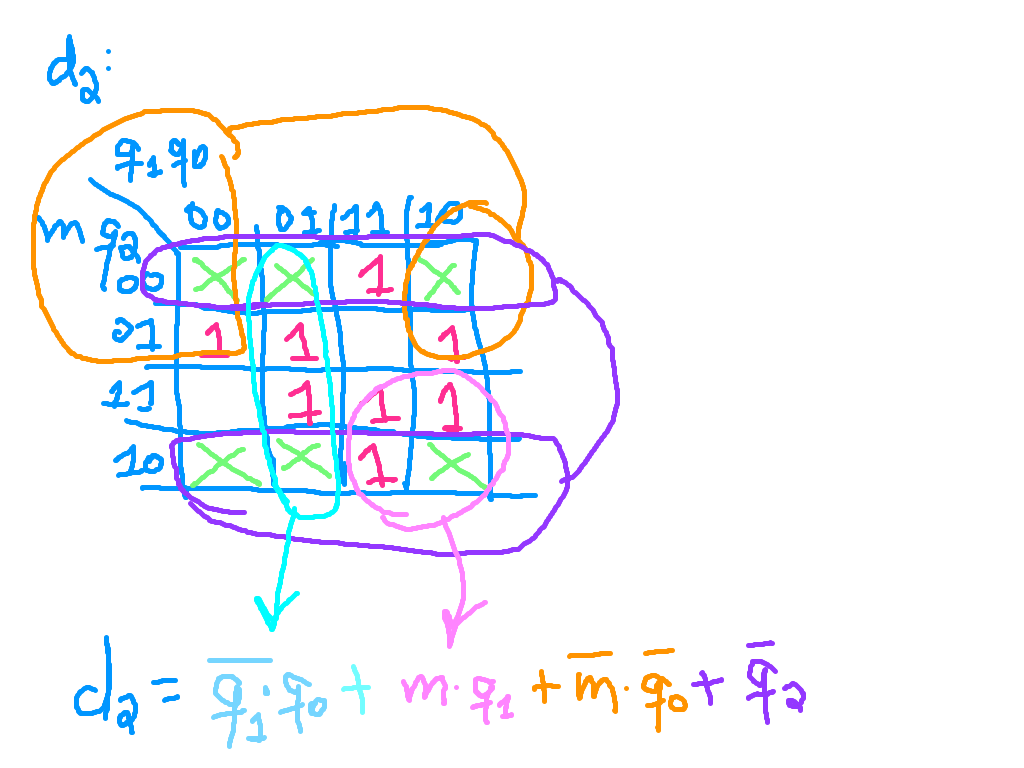

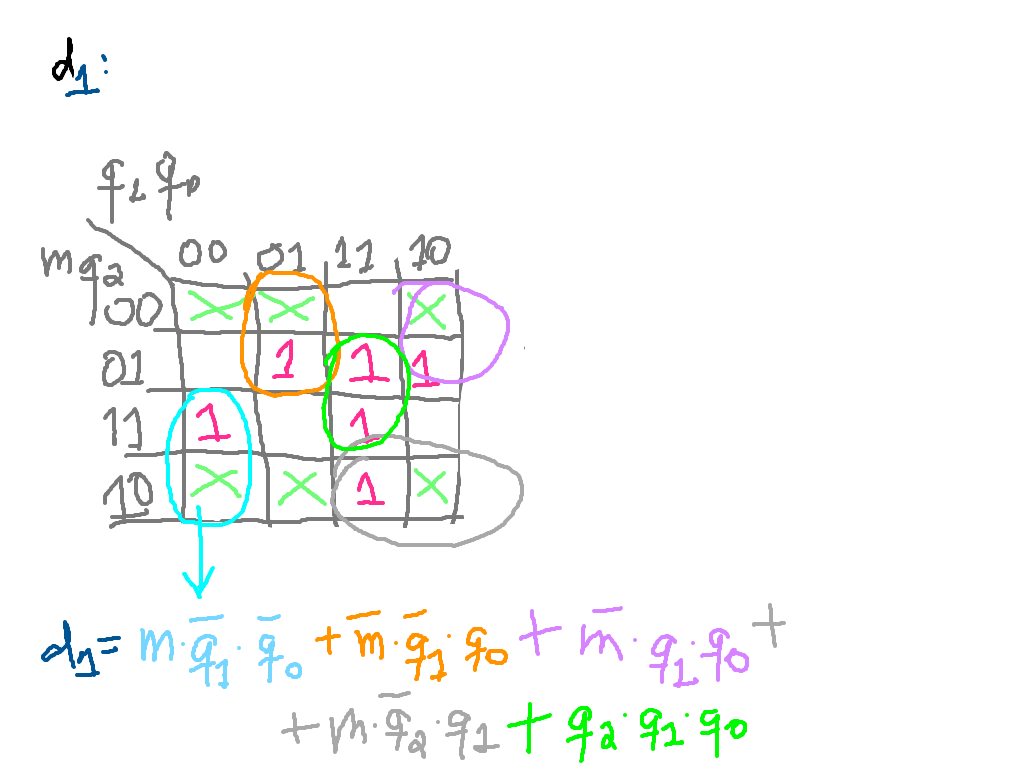

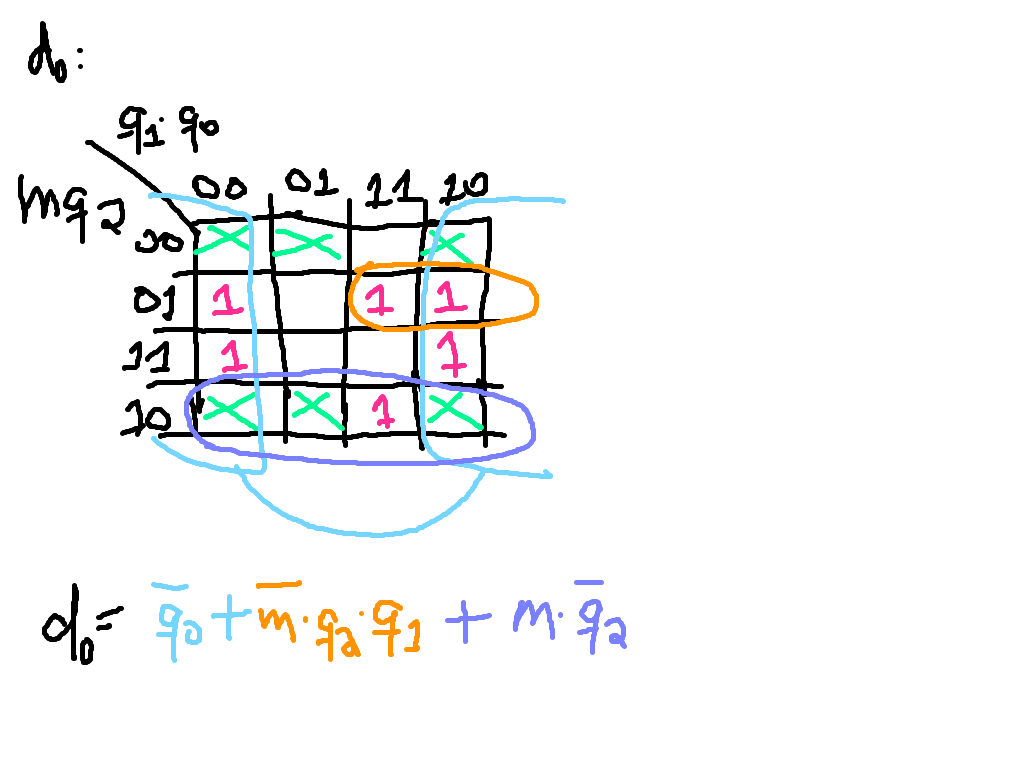

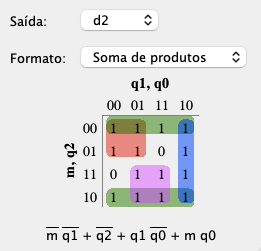

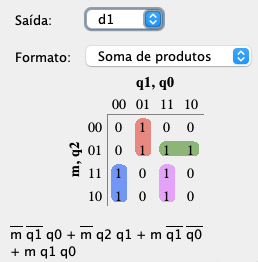

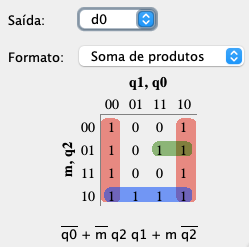

Seguem os Mapas de karnaught e equações para as entradas dos FF´s adotados neste projeto:

Isto implica usar: 1 OR(4) + 3 AND(2) + 3 NOT (a portas NOT geram: , e ).

Implica usar: 1 OR(5) + 5 AND(3) + 1.

Implica usar: 1 OR(3) + 1 AND(2) + 1 AND(3).

Total:

- 3 FF's D 2 74LS74;

- 1 OR(5) + 1 OR(4) + 1 OR(3) 2 74LS27 (3 NOR(3));

- 4 AND(2) 1 74LS08;

- 6 AND(3) 2 74LS11 (3 x AND(3));

- 5 NOT 1 74LS04;

Um total de 8 pastilhas TTL.

Próximo passo: desenhar o circuito lógico (diagrama elétrico).

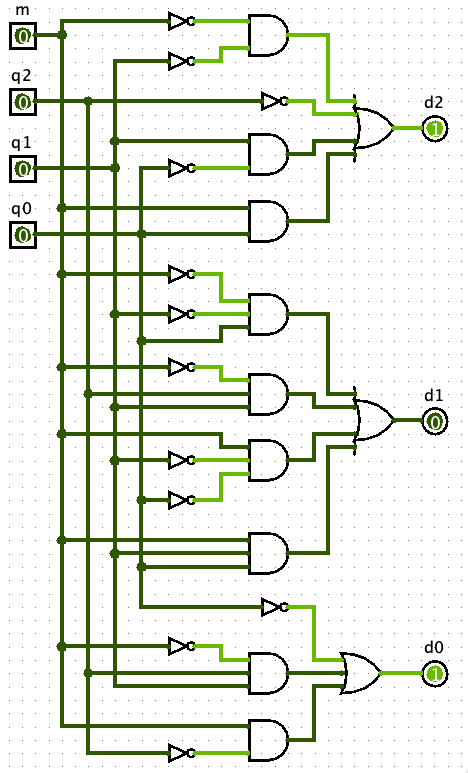

Mas... poderíamos ter usado o Logisim para realizar esta parte do projeto (a eletrônica digital combinacional necessária para comandar os FF's): arquivo: projeto_2024_1.circ . Neste caso, esta ferramenta nos sugere:

| D2: | D1: | D0: |

|---|---|---|

|  |  |

Percebemos que a solução sugerida para está melhor (implica: 1 OR(4) + 4 AND(3)).

O Logisim termina sugerindo o seguinte circuito para a eletrônica combinacional de comando dos FF's:

Obs.: Este circuito lógico, principalmente a eletrônica combinacional associada com a entrada (FF-1), exige um circuito algo grande.

Detalhes

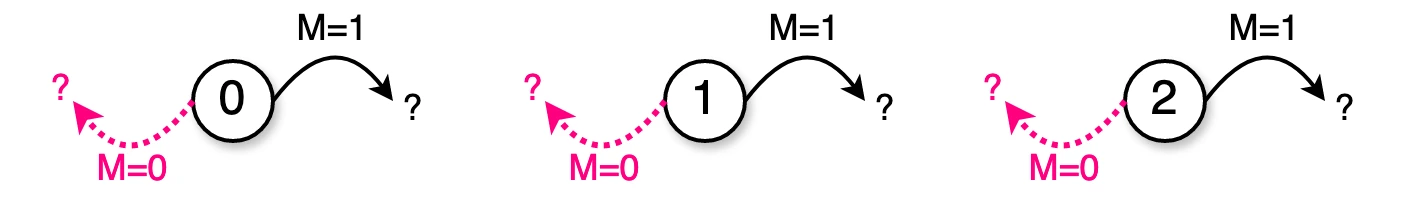

- O que acontece se o circuito anterior for inicializado no estado inicial 0, 1 e 2 ?

Isto é:

Resposta:

Considerando a lógica de controle dos FF's o circuito sugerido pelo Logisim, notamos que:

Caso do circuito partir em 0:

Caso :

- Analisando o Mapa K referente à D2, percebemos que este estado corresponde à célula e que a mesma foi incorporada num agrupamento, o que siginica que .

- Analisando o Mapa K referente à D1, percebemos que este estado corresponde à célula e que a mesma não foi incorporada num agrupamento, o que siginica que .

- Analisando o Mapa K referente à D0, percebemos que este estado corresponde à célula e que a mesma foi incorporada num agrupamento, o que siginica que .

- Resumindo, o próximo estado seria então, .

Caso :

- Analisando o Mapa K referente à D2, percebemos que este estado corresponde à célula e que a mesma foi incorporada num agrupamento, o que siginica que .

- Analisando o Mapa K referente à D1, percebemos que este estado corresponde à célula e que a mesma foi incorporada num agrupamento, o que siginica que .

- Analisando o Mapa K referente à D0, percebemos que este estado corresponde à célula e que a mesma foi incorporada num agrupamento, o que siginica que .

- Resumindo, o próximo estado seria então, .

Caso do circuito partir em 1:

Caso :

- Analisando o Mapa K referente à D2, percebemos que este estado corresponde à célula e que a mesma foi incorporada num agrupamento, o que siginica que .

- Analisando o Mapa K referente à D1, percebemos que este estado corresponde à célula e que a mesma foi incorporada num agrupamento, o que siginica que .

- Analisando o Mapa K referente à D2, percebemos que este estado corresponde à célula e que a mesma não foi incorporada num agrupamento, o que siginica que .

- Resumindo, o próximo estado seria então, .

Caso :

- Analisando o Mapa K referente à D2, percebemos que este estado corresponde à célula e que a mesma foi incorporada num agrupamento, o que siginica que .

- Analisando o Mapa K referente à D1, percebemos que este estado corresponde à célula e que a mesma não foi incorporada num agrupamento, o que siginica que .

- Analisando o Mapa K referente à D0, percebemos que este estado corresponde à célula e que a mesma foi incorporada num agrupamento, o que siginica que .

- Resumindo, o próximo estado seria então, .

Caso do circuito partir em 2:

Caso :

- Analisando o Mapa K referente à D2, percebemos que este estado corresponde à célula e que a mesma foi incorporada num agrupamento, o que siginica que .

- Analisando o Mapa K referente à D1, percebemos que este estado corresponde à célula e que a mesma não foi incorporada num agrupamento, o que siginica que .

- Analisando o Mapa K referente à D0, percebemos que este estado corresponde à célula e que a mesma foi incorporada num agrupamento, o que siginica que .

- Resumindo, o próximo estado seria então, .

Caso =1.

- Analisando o Mapa K referente à D2, percebemos que este estado corresponde à célula e que a mesma foi incorporada num agrupamento, o que siginica que .

- Analisando o Mapa K referente à D1, percebemos que este estado corresponde à célula e que a mesma não foi incorporada num agrupamento, o que siginica que 0.

- Analisando o Mapa K referente à D0, percebemos que este estado corresponde à célula e que a mesma foi incorporada num agrupamento, o que siginica que .

- Resumindo, o próximo estado seria então, .

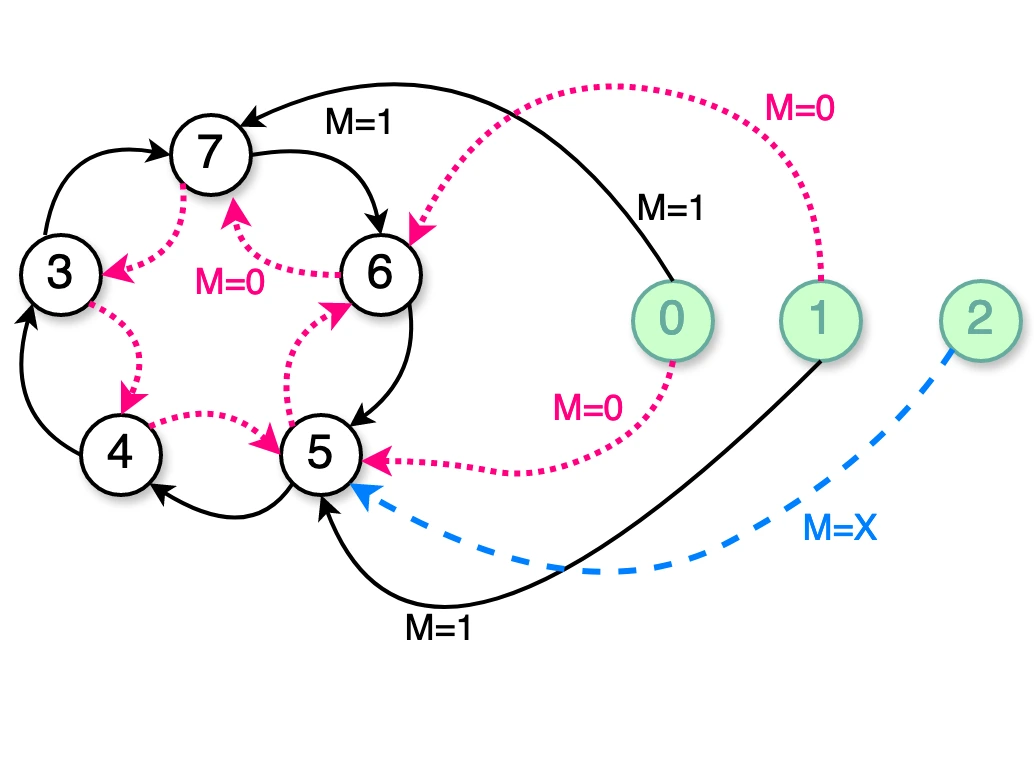

Resumindo, podemos compor o seguinte diagrama de estados final para este circuito:

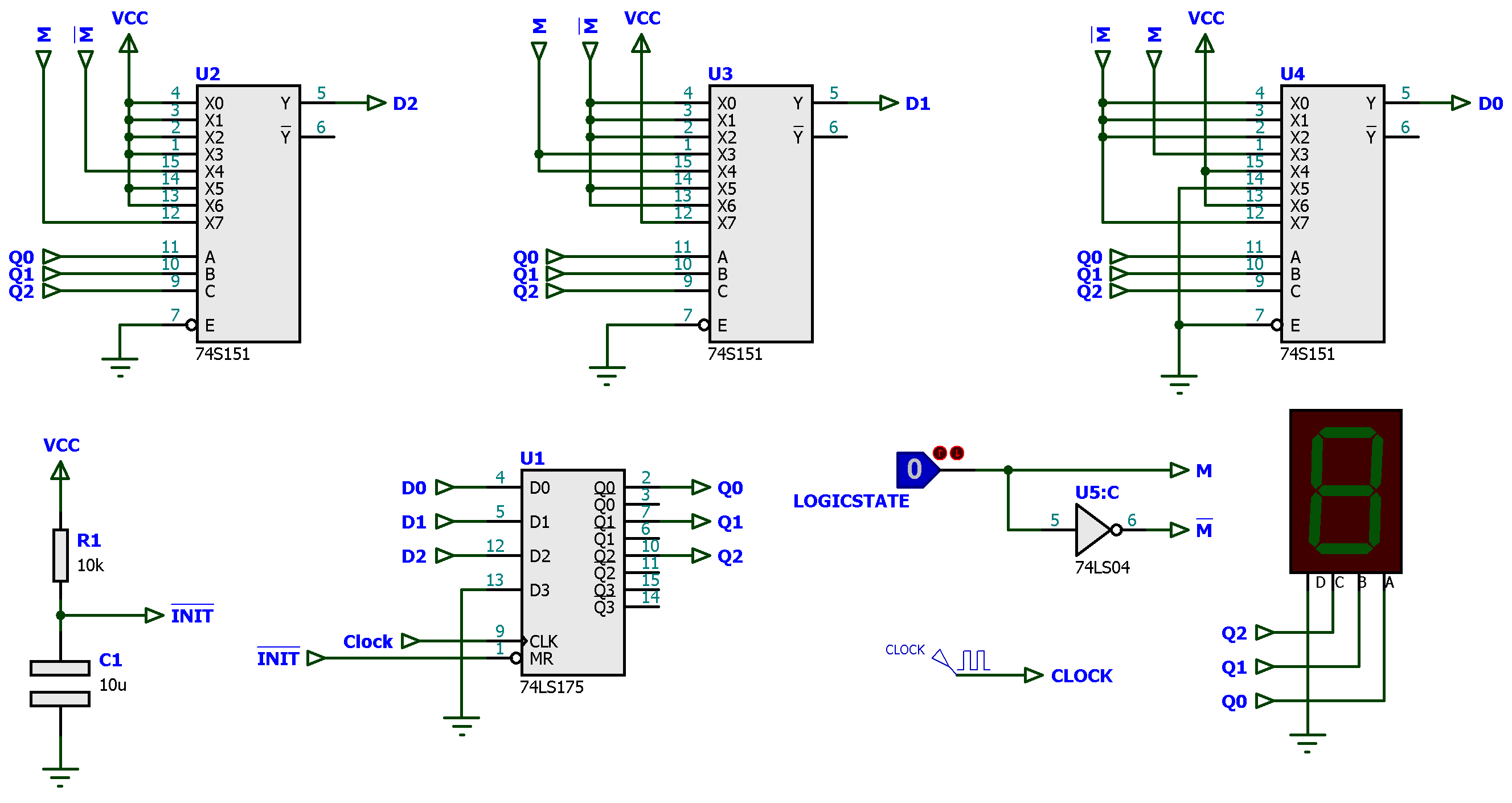

Outras soluções de circuito para lógica de controle:

Lembramos que podemos sinterizar uma função lógica combinacional usando MUX ou DEC. Se optarmos por MUX, seria necessário um MUX com 4 entradas de seleção (correspondendo as variáveis: , , e ), de 16 canais (uma pastilha algo grande, com 24 pinos), ou até podemos adaptar a solução para um MUX de 8 canais e usar a varíavel mais significativa, para completar a adaptação para circuito combinacional usando um MUX menor (de 8 canais; 16 pinos).

Temos então que deduzir a "programação" de cada um dos MUXes de 8 canais, um para cada circuito combinacional ncessário aqui (um para a entrada do FF-0, outro para entrada do FF-1 e o terceiro MUX associado com a entrada do FF-2).

Faremos isto na próxima aula (10/05/2024) e tentaremos simular este circuito no Proteus.

- Video desta parte da aula: projeto deste contador síncrono.

- Vídeo da primeira parte desta aula: teoria associada com projeto de contadores (ou máquinas) síncronas.

Obs.: para acessar estes videos eventualmente será necessário você autenticar sua conta @upf.br.

Continuação (aula de 10/05/2024)...

Resolvendo o circuito usando

- CI 74LS175 (4 FF's D);

- 3 MUXES de 8 canais (74LS151) + 1 porta NOT (74LS04) (associada com a variável ):

Note que neste caso, todas as transições de estado são "programadas", incluindo as "don´t care", ou seja, antes, tínhamos o projeto assim:

| Transições Definidas | Transições "don´t care" |

|---|---|

|  |

Agora necessitamos definir o que acontece se o circuito parte destes estados, porque não podemos programar as entras , e do MUX com um nível lóligo indeterminado

Neste caso, foi optado (deliberadamente) por definir como o circuito deve continuar à partir dos estados anteriores, resultando em:

Programando os MUXes:

xMUX para d2:| | S2 S1 S0 <-- Entradas Select do MUXRef | M | q2 q1 q0 | Q2 Q1 Q0 | d2 | Obs | Entradas MUX-----+---+----------+----------+-----+---------------+-------------0 | 0 | 0 0 0 | 1 1 1 | 1 | 0 --> 7 (M=0) | I0 = 11 | 0 | 0 0 1 | 1 1 1 | 1 | 1 --> 7 (M=0) | I1 = 12 | 0 | 0 1 0 | 1 1 1 | 1 | 2 --> 7 (M=0) | I2 = 1-----+---+----------+----------+-----+---------------+-------------3 | 0 | 0 1 1 | 1 0 0 | 1 | 3 --> 4 (M=0) | I3 = 14 | 0 | 1 0 0 | 1 0 1 | 1 | 4 --> 5 (M=0) | I4 = /M5 | 0 | 1 0 1 | 1 1 0 | 1 | 5 --> 6 (M=0) | I5 = 16 | 0 | 1 1 0 | 1 1 1 | 1 | 6 --> 7 (M=0) | I6 = 17 | 0 | 1 1 1 | 0 1 1 | 0 | 7 --> 3 (M=0) | I7 = M====================================================================8/0 | 1 | 0 0 0 | 1 0 0 | 1 | 0 --> 4 (M=1)9/1 | 1 | 0 0 1 | 1 0 0 | 1 | 1 --> 4 (M=1)10/2 | 1 | 0 1 0 | 1 0 0 | 1 | 2 --> 4 (M=1)-----+---+----------+----------+-----+---------------+-------------11/3 | 1 | 0 1 1 | 1 1 1 | 1 | 3 --> 7 (M=1)12/3 | 1 | 1 0 0 | 0 1 1 | 0 | 4 --> 3 (M=1)13/5 | 1 | 1 0 1 | 1 0 0 | 1 | 5 --> 4 (M=1)14/6 | 1 | 1 1 0 | 1 0 1 | 1 | 6 --> 5 (M=1)15/7 | 1 | 1 1 1 | 1 1 0 | 1 | 7 --> 6 (M=1)

xMUX para d1:| | S2 S1 S0 <-- Entradas Select do MUXRef | M | q2 q1 q0 | Q2 Q1 Q0 | d1 | Obs | Entradas MUX-----+---+----------+----------+----+---------------+-------------0 | 0 | 0 0 0 | 1 1 1 | 1 | 0 --> 7 (M=0) | I0 = /M1 | 0 | 0 0 1 | 1 1 1 | 1 | 1 --> 7 (M=0) | I1 = /M2 | 0 | 0 1 0 | 1 1 1 | 1 | 2 --> 7 (M=0) | I2 = /M-----+---+----------+----------+----+---------------+-------------3 | 0 | 0 1 1 | 1 0 0 | 0 | 3 --> 4 (M=0) | I3 = M4 | 0 | 1 0 0 | 1 0 1 | 0 | 4 --> 5 (M=0) | I4 = M5 | 0 | 1 0 1 | 1 1 0 | 1 | 5 --> 6 (M=0) | I5 = /M6 | 0 | 1 1 0 | 1 1 1 | 1 | 6 --> 7 (M=0) | I6 = /M7 | 0 | 1 1 1 | 0 1 1 | 1 | 7 --> 3 (M=0) | I7 = 1==================================================================8/0 | 1 | 0 0 0 | 1 0 0 | 0 | 0 --> 4 (M=1)9/1 | 1 | 0 0 1 | 1 0 0 | 0 | 1 --> 4 (M=1)10/2 | 1 | 0 1 0 | 1 0 0 | 0 | 2 --> 4 (M=1)-----+---+----------+----------+----+---------------+-------------11/3 | 1 | 0 1 1 | 1 1 1 | 1 | 3 --> 7 (M=1)12/4 | 1 | 1 0 0 | 0 1 1 | 1 | 4 --> 3 (M=1)13/5 | 1 | 1 0 1 | 1 0 0 | 0 | 5 --> 4 (M=1)14/6 | 1 | 1 1 0 | 1 0 1 | 0 | 6 --> 5 (M=1)15/7 | 1 | 1 1 1 | 1 1 0 | 1 | 7 --> 6 (M=1)

xMUX para d0:| | S2 S1 S0 <-- Entradas Select do MUXRef | M | q2 q1 q0 | Q2 Q1 Q0 | d0 | Obs | Entradas MUX-----+---+----------+----------+----+---------------+-------------0 | 0 | 0 0 0 | 1 1 1 | 1 | 0 --> 7 (M=0) | I0 = /M1 | 0 | 0 0 1 | 1 1 1 | 1 | 1 --> 7 (M=0) | I1 = /M2 | 0 | 0 1 0 | 1 1 1 | 1 | 2 --> 7 (M=0) | I2 = /M-----+---+----------+----------+----+---------------+-------------3 | 0 | 0 1 1 | 1 0 0 | 0 | 3 --> 4 (M=0) | I3 = M4 | 0 | 1 0 0 | 1 0 1 | 1 | 4 --> 5 (M=0) | I4 = 15 | 0 | 1 0 1 | 1 1 0 | 0 | 5 --> 6 (M=0) | I5 = 06 | 0 | 1 1 0 | 1 1 1 | 1 | 6 --> 7 (M=0) | I6 = 17 | 0 | 1 1 1 | 0 1 1 | 1 | 7 --> 3 (M=0) | I7 = /M==================================================================8/0 | 1 | 0 0 0 | 1 0 0 | 0 | 0 --> 4 (M=1)9/1 | 1 | 0 0 1 | 1 0 0 | 0 | 1 --> 4 (M=1)10/2 | 1 | 0 1 0 | 1 0 0 | 0 | 2 --> 4 (M=1)-----+---+----------+----------+----+---------------+-------------11/3 | 1 | 0 1 1 | 1 1 1 | 1 | 3 --> 7 (M=1)12/4 | 1 | 1 0 0 | 0 1 1 | 1 | 4 --> 3 (M=1)13/5 | 1 | 1 0 1 | 1 0 0 | 0 | 5 --> 4 (M=1)14/6 | 1 | 1 1 0 | 1 0 1 | 1 | 6 --> 5 (M=1)15/7 | 1 | 1 1 1 | 1 1 0 | 0 | 7 --> 6 (M=1)

Obs.: durante resolução sem aula, a programação para as linhas Ref = 12, 13 e 15 estava equivocada!

Diagrama elétrico e simulação:

Este circuito ( contador_diferente_2024_1.pdsprj - Proteus 8.13 SP0 ) ocupa simplesmente 5 pastilhas.

Segue uma simulação:

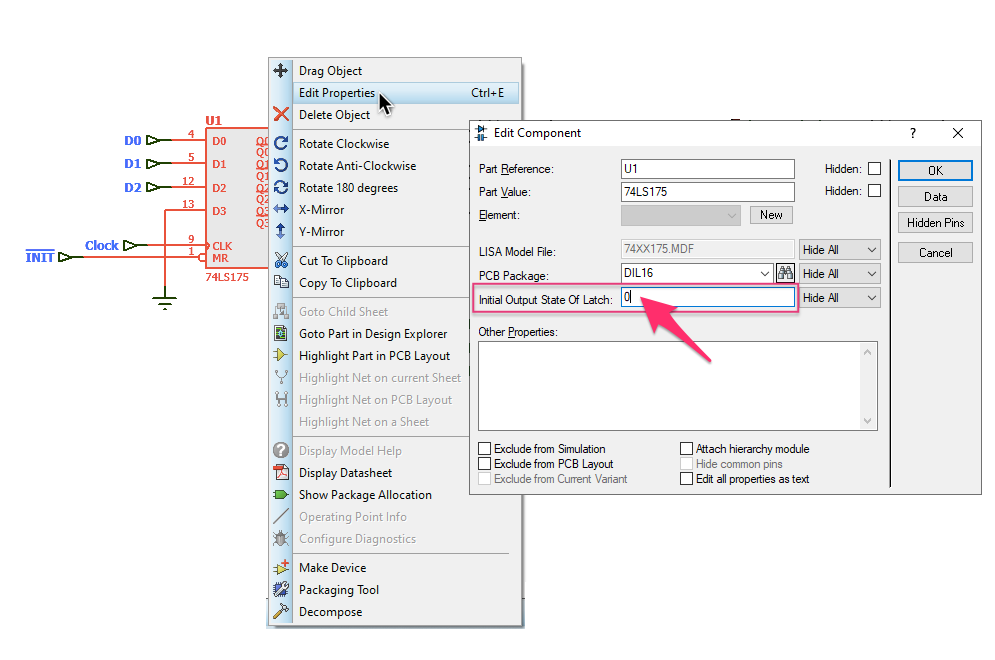

Detalhe: a pastilha 74LS175 não permite um "Parallel Load", isto é, não permite inicializar seus FF´s em qualquer estado. Temos disponível apenas o Master Reset (pino ).

O Proteus permite forçar a inicialização da pastilha 74LS175, se, depois de selecionarmos a mesma (botão direito do mouse sobre a pastilha), selecionamos Propriedades e alteramos o valor da caixa de texto "Inicial Output State of Lath" para o valor desejado (no caso, por padrão, estão o valor ). Ver figura abaixo:

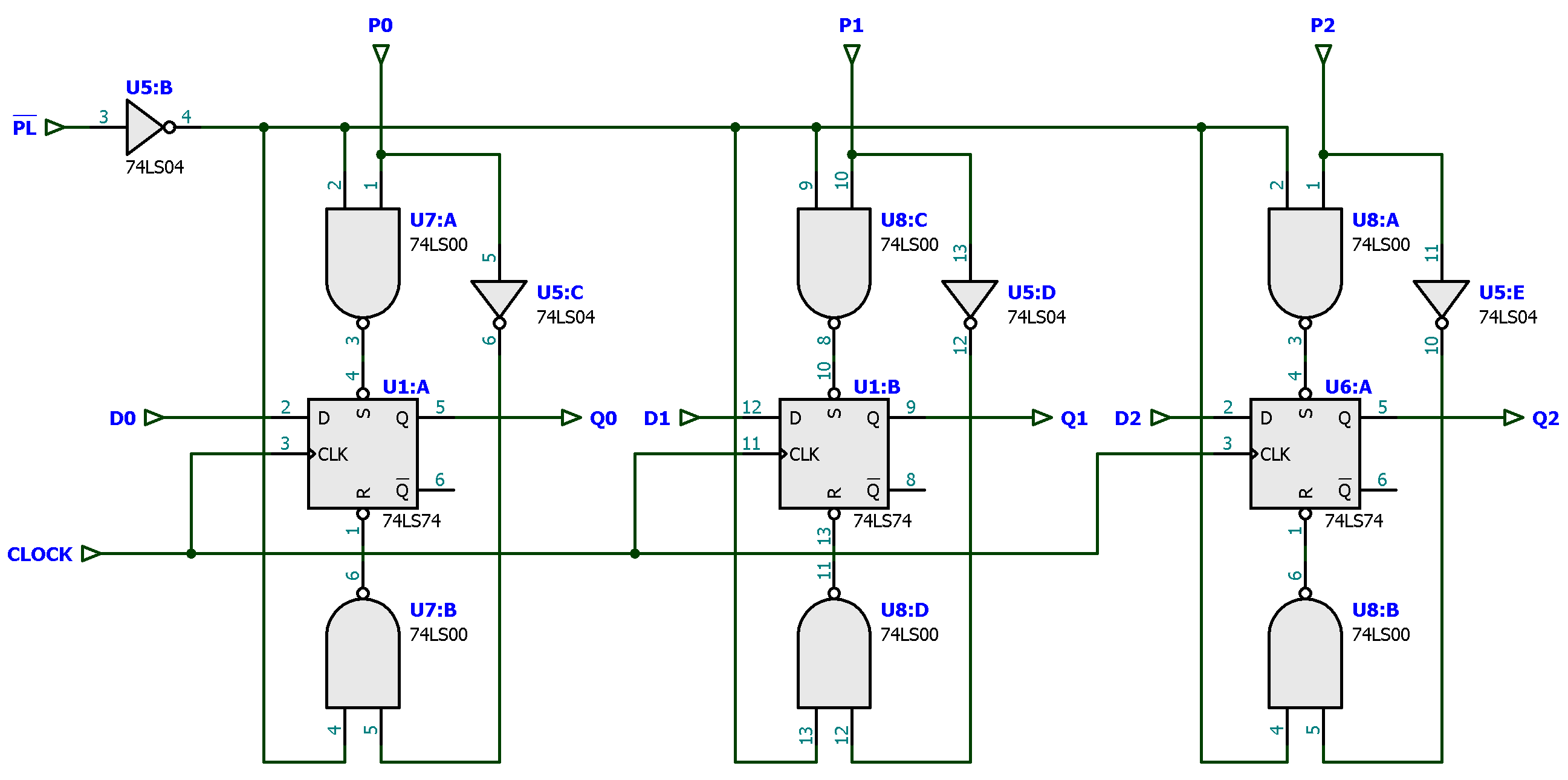

Ou podemos optar por criar um circuito usando pastilhas 74LS74 + outras portas lógicas básicas para incorporar uma função similar ao "Parallel Load":

Mais ums poucas modificações no circuito anterior e então teremos:

Esta última solução ( circuito: contador_diferente_2024_1_PL.pdsprj ) exige 8 pastilhas.

Fernando Passold, em 03/05/2024.